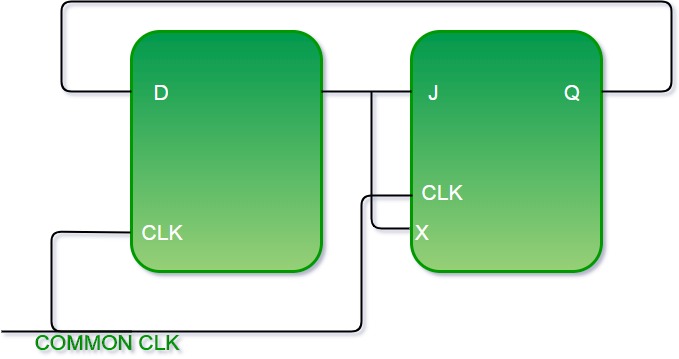

Un flip-flop D activado por flanco positivo se conecta a un flip-flop JK activado por flanco positivo de la siguiente manera. La salida Q del flip-flop D está conectada a las entradas J y K del flip-flop JK, mientras que la salida Q del flip-flop JK está conectada a la entrada del flip-flop D. Inicialmente, la salida del flip-flop D se establece en uno lógico y la salida del flip-flop JK se borra. ¿Cuál de las siguientes es la secuencia de bits (incluido el estado inicial) generada en la salida Q del flip-flop JK cuando los flip-flops están conectados a un reloj común de funcionamiento libre? Suponga que J = K = 1 es el modo de alternancia y J = K = 0 es el modo de retención de estado del flip-flop JK. Ambos flip-flops tienen retrasos de propagación distintos de cero.

(A) 0110110…

(B) 0100100…

(C)011101110…

(D) 011001100…

Inicialmente salida Q de D – FF = 1

Inicialmente salida Q de JK – FF = 0

Ahora, con la ayuda del estado actual y la siguiente tabla de estado, podemos ver lo que sucede en el circuito.

- Alternar: J = K = 1

- Mantener: J = K = 0

Vemos en la tabla Q que la salida de D-FF va a la siguiente entrada de estado de JK-FF y la secuencia de bits producida es como 110110…..

Incluyendo la condición inicial (0), obtenemos una salida como 0110110110….

Por lo tanto, la respuesta es (A) parte.

Otra explicación:

Aquí, se da que el flip flop JK alternará cuando J = K = 1 y retendrá la salida si J = K = 0.

Además, la salida del flip flop D seguirá siendo la misma que la entrada.

Entonces tenemos

Salida inicial: D = 1

JK = 0

After clock 1 : D = 0 (D gets 0 as input from initial output of JK, so output = 0)

JK = 1 (J = K = 1 desde la salida inicial de D, por lo que la salida cambiaría de 0 a 1)

After clock 2 : D = 1 (D gets 1 as input from previous output of JK, so output = 1)

JK = 1 (J = K = 0 de la salida anterior de D, por lo que la salida se mantendría en 1)

After clock 3 : D = 1 (D gets 1 as input from previous output of JK, so output = 1)

JK = 0 (J = K = 1 de la salida anterior de D, por lo que la salida cambiaría de 1 a 0)

After clock 4 : D = 0 (D gets 0 as input from previous output of JK, so output = 0)

JK = 1 (J = K = 1 de la salida anterior de D, por lo que la salida cambiaría de 0 a 1)

After clock 5 : D = 1 (D gets 1 as input from previous output of JK, so output = 1)

JK = 1 (J = K = 0 de la salida anterior de D, por lo que la salida se mantendría en 1)

Así, la secuencia de bits generada en la salida Q del flip flop JK será 0110110…

Publicación traducida automáticamente

Artículo escrito por GeeksforGeeks-1 y traducido por Barcelona Geeks. The original can be accessed here. Licence: CCBY-SA