Verilog , que significa Verificar lógica. Es ampliamente utilizado en la programación de dispositivos de hardware, con el aumento de las demandas de System Of Chips y dispositivos de hardware Verilog HDL ha crecido en popularidad. En Verilog, el diseño y la verificación de los dispositivos digitales en el nivel de abstracción RTL se ha vuelto menos complejo. Comprender Verilog es lo mismo que programar en C, ya que tiene la mayor parte de la sintaxis similar.

Con el aumento de la demanda de VLSI, los diseños de chips han crecido en número. En los días iniciales, era difícil sintetizar la lógica y depurar el código. Así nació el lenguaje de descripción de hardware. El último estándar Verilog HDL ha hecho un cambio significativo en la programación HDL al hacer que el diseño sea lógicamente sintetizable y fácil de depurar. Ahora escribiremos nuestro primer programa Verilog e instalaremos Verilog en el Kernel de Linux.

Instalación de Verilog HDL en Linux

Icarus Verilog es una herramienta de simulación y síntesis de Verilog. Con esta herramienta, funciona como el compilador de Verilog en un formato de destino específico. Este compilador puede generar un formulario intermedio llamado ensamblaje vvp para la simulación por lotes y este formulario intermedio se ejecuta con la ayuda del comando «vvp». Para la síntesis, el compilador genera netlists en el formato deseado.

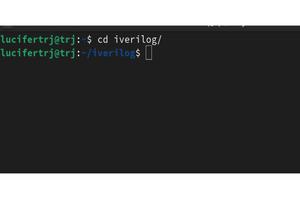

Paso 1: clone el repositorio Icarus Verilog localmente. Clone Icarus Verilog Repository: git clone https://github.com/steveicarus/iverilog.git. Una vez que clone el repositorio, se crea un directorio con el nombre iverilog, ahora use el comando cd para cambiar el directorio de trabajo actual.

clon de git https://github.com/steveicarus/iverilog.git

disco compacto

Paso 2: Configurar archivos. Una vez que esté dentro del directorio iverilog, hay muy pocos pasos para configurar. Para configurar el iverilog en su repositorio local, ejecute el siguiente comando.

sh autoconf.sh

Si se encuentra con un error, significa que autoconf no se ha instalado en su sistema. Instale autoconf ingresando el siguiente comando.

Fedora: sudo dnf instalar autoconf

Ubuntu: sudo apt-get install autoconf

El mensaje de configuración exitosa se ve así:

Autoconf en root…

Precompilación de lexor_keyword.gperf

Precompilación de vhdlpp/lexor_keyword.gperf

Y luego configure los archivos para actualizar la configuración predeterminada.

./configurar

Ahora ya está listo para trabajar.

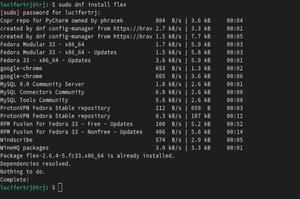

Paso 3: Instale iverilog y GTKWave. Una vez que configure la configuración predeterminada, acceda al directorio raíz y ejecute el comando make install. Pero antes de eso, asegúrese de tener instalados GCC, g ++, bison y flex. Dado que Verilog se creó utilizando la programación C: se deben instalar g ++, gcc, flex y bison para compilar y ejecutar el código de iverilog. Si no tiene gcc, g++, bison y flex, ejecute estos comandos.

//sudo apt-get install nombre_del_paquete en ubuntu

sudo dnf instalar flex

sudo dnf instalar gcc

sudo dnf instalar bisonte

sudo dnf instalar g ++

Una vez que tenga estos elementos esenciales instalados, proceda a realizar la instalación.

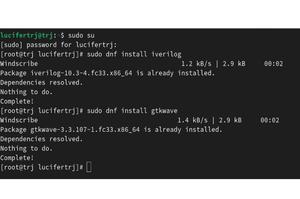

sudo su

hacer instalar

sudo dnf instalar iverilog

sudo dnf instalar gtkwave

El iverilog se instaló correctamente, ahora escribamos el código Verilog y ejecútelo.

Compilar y ejecutar código Verilog

Escribiremos un código de compuerta simple tanto de diseño como de simulación. Asegúrese de guardar Verilog con la extensión .v. La tabla de verdad es:

| a | b | afuera |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Primero, cree un nombre de archivo como dut.v, que es nuestro diseño bajo el bloque de código de prueba. Comenzamos con la definición de un nombre de módulo que comienza con un módulo de palabra clave de módulo. Pasamos una lista de puertos como argumento para el nombre del módulo. Uso de modelos de abstracción de flujo de datos.

//dut= guardar en dut.v

módulo and_gate(fuera,a,b);

entrada a,b;

salida;

asignar fuera = a & b;

//y a1(fuera,a,b); para abstracción a nivel de puerta

módulo final

A continuación, escriba el banco de pruebas o el código de simulación. La simulación consiste en verificar el bloque de diseño al proporcionarle información.

// banco de pruebas para y puerta

módulo tb;

registro A, B; //entrada asignada para registrar

alambrar; //salida asignada a la red

//instanciar dut

and_gate dut(salida,A,B);

inicial

empezar

A = 0; B = 0;#10

$pantalla(“A=%b B=%b Salida=%b”,A,B,fuera);

A = 0; B = 1;#10

$display(“A=%b B=%d Salida=%b”,A,B,fuera);

A = 1; B = 0;#10

$pantalla(“A=%b B=%b Salida=%b”,A,B,fuera);

A = 1; B = 1;#10

$pantalla(“A=%b B=%b Salida=%b”,A,B,fuera);

$terminar;

final

módulo final

La siguiente sintaxis se utiliza para compilar y ejecutar el código Verilog:

//compilar:

iverilog -o check_code tb.v dut.v

//correr:

vvp check_code

Producción:

Puede verificar la salida consultando la tabla de verdad