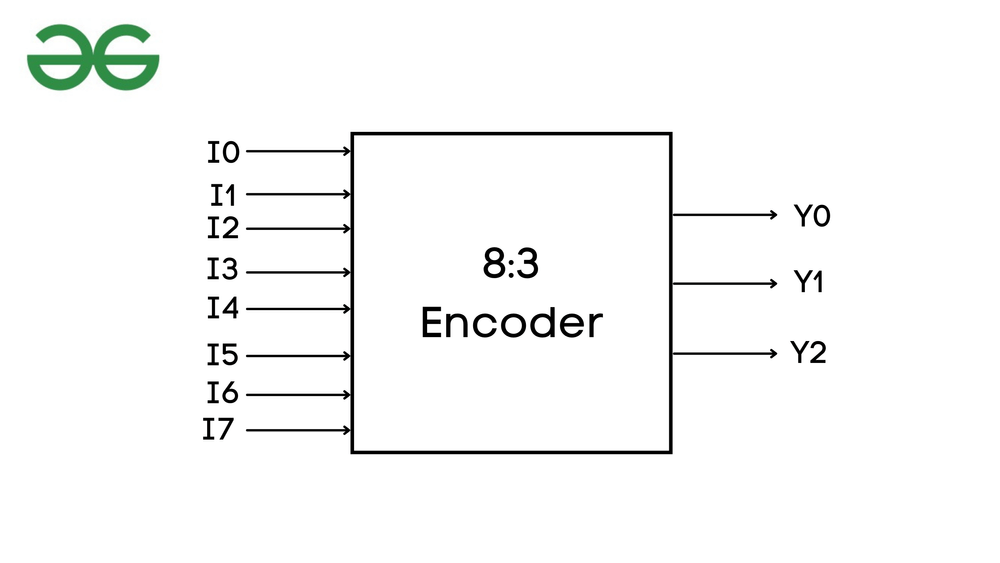

En el circuito del sistema digital, un codificador es un circuito combinacional que toma 2 n líneas de señal de entrada y las codifica en n líneas de señal de salida. Cuando la habilitación es verdadera, es decir, las líneas de señal de entrada correspondientes muestran la salida de bit binario equivalente.

Por ejemplo, el codificador 8:3 tiene 8 líneas de entrada y 3 líneas de salida, el codificador 4:2 tiene 4 líneas de entrada y 2 líneas de salida, y así sucesivamente.

Un codificador de prioridad 8:3 tiene siete líneas de entrada, es decir, i0 a i7, y tres líneas de salida y2, y1 e y0. En 8:3 Priority Encoder i7 tiene la prioridad más alta e i0 la más baja.

Mesa de la verdad:

|

Aporte |

Producción |

||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| es | i7 | i6 | i5 | i4 | i3 | i2 | i1 | i0 | y2 | y1 | y0 |

| 0 | X | X | X | X | X | X | X | X | z | z | z |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | X | 0 | 0 | 1 |

| 1 | 0 | 0 | 0 | 0 | 0 | 1 | X | X | 0 | 1 | 0 |

| 1 | 0 | 0 | 0 | 0 | 1 | X | X | X | 0 | 1 | 1 |

| 1 | 0 | 0 | 0 | 1 | X | X | X | X | 1 | 0 | 0 |

| 1 | 0 | 0 | 1 | X | X | X | X | X | 1 | 0 | 1 |

| 1 | 0 | 1 | X | X | X | X | X | X | 1 | 1 | 0 |

| 1 | 1 | X | X | X | X | X | X | X | 1 | 1 | 1 |

Símbolo lógico:

Implemente el codificador de prioridad en el código de Verilog:

La mayor parte de la programación se ocupa del desarrollo y diseño de software, pero Verilog HDL es un lenguaje de descripción de hardware que se utiliza para diseñar el diseño electrónico. Verilog proporciona a los diseñadores el diseño de los dispositivos en función de diferentes niveles de abstracción que incluyen: nivel de puerta, flujo de datos, nivel de interruptor y modelado de comportamiento.

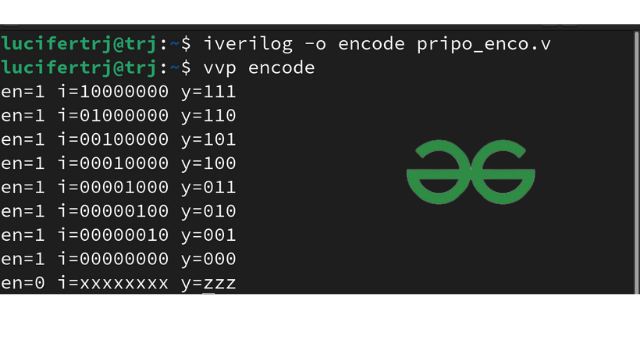

Modelado de comportamiento:

Modelo de comportamiento, que es el nivel más alto de abstracción. Dado que estamos utilizando Modelado de comportamiento, escribiremos el código usando if-else para garantizar los valores de entrada del Codificador de prioridad. Al usar la condición if, los valores de salida se asignan en función de la prioridad.

Bloque de diseño: modelado de comportamiento

module priorityencoder_83(en,i,y);

// declare

input en;

input [7:0]i;

// store and declare output values

output reg [2:0]y;

always @(en,i)

begin

if(en==1)

begin

// priority encoder

// if condition to chose

// output based on priority.

if(i[7]==1) y=3'b111;

else if(i[6]==1) y=3'b110;

else if(i[5]==1) y=3'b101;

else if(i[4]==1) y=3'b100;

else if(i[3]==1) y=3'b011;

else if(i[2]==1) y=3'b010;

else if(i[1]==1) y=3'b001;

else

y=3'b000;

end

// if enable is zero, there is

// an high impedance value.

else y=3'bzzz;

end

endmodule

Banco de pruebas: Comportamiento

Un Testbench es un bloque de simulación que se utiliza para proporcionar entradas al bloque de diseño. La mejor manera de escribir Testbench es tener una buena percepción de la tabla de verdad. Una vez que tenga lista la tabla de verdad, proporcione los valores de entrada dentro del banco de pruebas.

module tb;

reg [7:0]i;

reg en;

wire [2:0]y;

// instantiate the model: creating

// instance for block diagram

priorityenoder_83 dut(en,i,y);

initial

begin

// monitor is used to display the information.

$monitor("en=%b i=%b y=%b",en,i,y);

// since en and i are input values,

// provide values to en and i.

en=1; i=128;#5

en=1; i=64;#5

en=1; i=32;#5

en=1; i=16;#5

en=1; i=8;#5

en=1; i=4;#5

en=1; i=2;#5

en=1; i=0;#5

en=0;i=8'bx;#5

$finish;

end

endmodule

Producción:

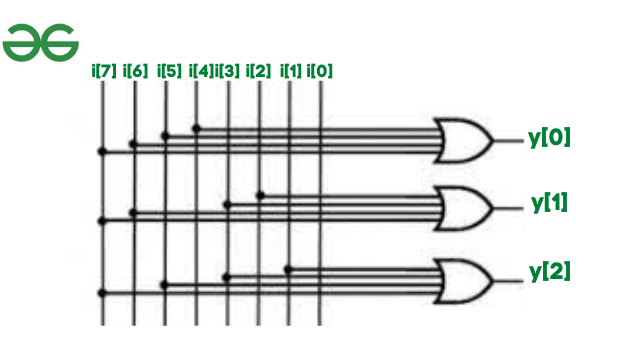

Modelado de flujo de datos:

En el modelado de flujo de datos, definimos la salida, es decir, net, asignando valores de entrada, es decir, reg, usando palabras clave asignadas. Para escribir el modelado de flujo de datos y el modelado a nivel de puerta, necesitamos un diagrama lógico para formar conexiones.

Aquí está el diagrama lógico del codificador de prioridad 8:3

Modelado de flujo de datos

Bloque de diseño: flujo de datos

module priorityenoder83_dataflow(en,i,y);

// declare port list via input and output

input en;

input [7:0]i;

output [2:0]y;

// check the logic diagram and assign the outputs

assign y[2]=i[4] | i[5] | i[6] | i[7] &en;

assign y[1]=i[2] | i[3] | i[6] | i[7] &en;

assign y[0]=i[1] | i[3] | i[5] | i[7] &en;

endmodule

Banco de pruebas: Flujo de datos

module tb;

reg en;

reg [7:0]i;

wire [2:0]y;

// instantiate the model: creating

// instance for block diagram

priorityenoder83_dataflow dut(en,i,y);

initial

begin

// monitor is used to display the information.

$monitor("en=%b i=%b y=%b",en,i,y);

// since en and i are input values,

// provide values to en and i.

en=1;i=128;#5

en=1;i=64;#5

en=1;i=32;#5

en=1;i=16;#5

en=1;i=8;#5

en=1;i=4;#5

en=1;i=2;#5

en=1;i=1;#5

en=0;i=8'bx;#5

$finish;

end

endmodule

Producción:

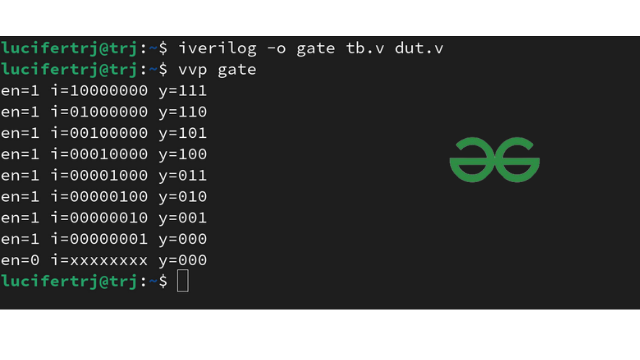

Modelado de nivel de puerta:

En el modelado a nivel de puerta, utilizamos puertas lógicas digitales utilizadas en electrónica digital.

Sintaxis:

logicgate object(out,in1,in2);

Ejemplo:

and a1(out,a,b);

Bloque de diseño: nivel de puerta

module priorityenoder83_gate(en,i,y);

// declare port list via input and output

input en;

input [7:0]i;

output [2:0]y;

wire temp1,temp2,temp3; // temp is used to apply

// enable for the or gates

// check the logic diagram and use

// logic gates to compute outputs

or o1(temp1,i[4],i[5],i[6],i[7]);

or o2(temp2,i[2],i[3],i[6],i[7]);

or o3(temp3,i[1],i[3],i[5],i[7]);

and a1(y[2],temp1,en);

and a2(y[1],temp2,en);

and a3(y[0],temp3,en);

endmodule

Banco de pruebas: nivel de puerta

module tb;

reg en;

reg [7:0]i;

wire [2:0]y;

// instantiate the model: creating

// instance for block diagram

priorityenoder83_gate dut(en,i,y);

initial

begin

// monitor is used to display

// the information.

$monitor("en=%b i=%b y=%b",en,i,y);

// since en and i are input values,

// provide values to en and i.

en=1;i=128;#5

en=1;i=64;#5

en=1;i=32;#5

en=1;i=16;#5

en=1;i=8;#5

en=1;i=4;#5

en=1;i=2;#5

en=1;i=1;#5

en=0;i=8'bx;#5

$finish;

end

endmodule

Producción:

Aplicación del codificador de prioridad:

- vehículos robóticos

- Sistemas de vigilancia de la salud en Hospitales