El Alpha 21064 es un microprocesador que fue desarrollado en 1992 por una empresa llamada Digital Equipment Corporation. A veces también se lo conoce como EV4, que era su nombre en clave. Este microprocesador fue una actualización de su predecesor EV3, que se fabricó utilizando el proceso CMOS-3 de 1,0 micrómetros de Digital. Sin embargo, EV4 se fabricó mediante un proceso CMOS-4 de 0,75 micrómetros. Esta tecnología de fabricación se consideró una innovación revolucionaria que lo ayudó a coronarse como el microprocesador más rápido en ese momento. Pronto, IBM lanzó el POWER2 multichip, que luego se convirtió en el microprocesador más rápido.

Arquitectura Alpha AXP:

La arquitectura Alpha AXP proporcionó un gran espacio de direcciones lineales de 64 bits. También ofrecía un sistema operativo completo de 64 bits con DEC OSF/1. Como era una arquitectura de 64 bits, evitó el equipaje de hardware que podría haber incluido instrucciones huérfanas de 32 bits y otros problemas de compatibilidad. Esta arquitectura también evitó los códigos de condición, los registros especiales, las instrucciones suprimidas y las instrucciones de ranura de retardo de bifurcación. De manera similar, también evitó el soporte de hardware directo para funciones que limitarían el rendimiento del sistema anticipado a través de la restricción del tiempo de ciclo. El diseño proporciona soporte mediante asistencia de software para una funcionalidad completa. Todos los datos se mueven entre los registros y la memoria sin computación.

- Direccionamiento: el AXP empleaba direccionamiento de bytes little-endian, que era muy similar a las computadoras Intel X86 y VAX. Usando las instrucciones de manipulación de bytes con una sola modificación de instrucción a la secuencia, los sistemas podrían acceder a datos grandes y pequeños. El AXP también hace el mapeo de direcciones virtuales a físicas por página, y sus páginas son de 8 Kbytes.

- Tipos de datos: la unidad de datos de la arquitectura era una palabra cuádruple de 64 bits, pero también admitía palabras largas de 32 bits. Los tipos de datos de coma flotante incluían formatos IEEE y VAX en formatos de precisión simple de 32 bits y doble precisión de 64 bits. Los tipos de datos de bytes y palabras no estaban respaldados por instrucciones directas de carga y almacenamiento, sino por una secuencia corta de instrucciones.

El alfa 21064:

Alpha 21064 fue la primera implementación de la arquitectura Alpha AXP. Tenía 1,68 millones de transistores. Este fue un microprocesador bien diseñado que proporcionó un alto rendimiento a través de la operación superescalar con un ciclo de reloj interno de frecuencia excepcionalmente alta. También tenía un reloj de sistema programable en el chip que ayudó a acomodar fácilmente una variedad de diseños de sistemas. El diseño del sistema podría ejecutar la CPU entre dos y ocho veces la frecuencia del reloj del sistema. Los dos factores controlados por el diseñador del microprocesador son el tiempo de ciclo y el número de instrucciones completadas por ciclo.

Arquitectura :

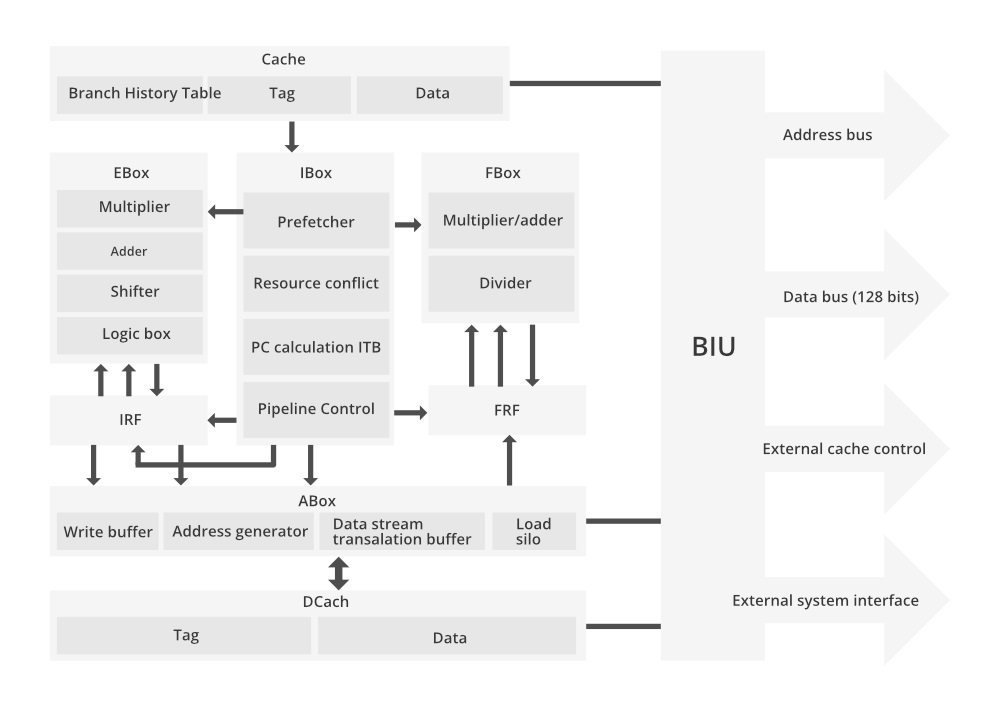

- Canalización: Hay dos canalizaciones: canalizaciones enteras y de punto flotante. La canalización de enteros tiene 7 etapas, mientras que la canalización de punto flotante tiene 10 etapas. Las primeras 4 etapas son comúnmente compartidas por ambos. Cada etapa puede procesar hasta 2 instrucciones en paralelo. El procesador obtiene un par de instrucciones en cada ciclo de la caché de instrucciones de 8 Kbytes en la etapa de obtención de instrucciones (IF). La etapa de intercambio controla la obtención previa de instrucciones, la predicción de bifurcaciones y el cálculo del índice de caché. Las dependencias de intrafetch se verifican en la etapa de emisión cero (I0). También completa la decodificación y configuración para la etapa número uno (I1). Los archivos de registro de números enteros y de punto flotante se leen en la etapa de emisión uno. Proporcionan datos para el cálculo de números enteros, punto flotante, carga y rama.

- Unidad de enteros: La unidad de enteros consiste en el archivo de registro de enteros (IRF) y el Ebox. El IRF contiene treinta y dos registros de propósito general de 64 bits. Tiene 6 puertos en total: cuatro de lectura y dos de escritura para permitir la ejecución paralela de cálculos de enteros y operaciones de carga, almacenamiento y bifurcación. Las unidades dedicadas de sumador, desplazador, multiplicador y lógica se incluyen en la ruta de datos. Las unidades sumadoras y lógicas proporcionan resultados en un ciclo. Sin embargo, la palanca de cambios requiere dos ciclos para obtener resultados. El cambiador está completamente canalizado, pero el multiplicador no está canalizado para ahorros de área.

- Unidad de punto flotante: La unidad de punto flotante consta de F-box y FRF. Su unidad combina latencias cortas con el máximo rendimiento. Contiene una entrada de 32 bits por un archivo de registro de 64 bits con dos puertos de escritura y tres puertos de lectura. Se puede iniciar un nuevo ciclo de instrucción cada ciclo con operaciones dependientes que requieren una latencia de seis ciclos. El objetivo de tiempo de ciclo rápido se traduce en una latencia total más larga medida en ciclos.

- Unidad de dirección: la unidad de dirección también se conoce como Abox. Realiza todas las operaciones de carga y almacenamiento. Contiene un sumador de desplazamiento dedicado para hacerlo en paralelo con otras unidades. También tiene un búfer de búsqueda de traducción de datos de 32 entradas. Esta unidad permite rangos de 8 Kbytes, 64 Kbytes, 512 Kbytes o 4 MB para cada entrada. La unidad de dirección también puede bloquear instrucciones independientes. El búfer de escritura combina datos de tiendas adyacentes para reducir los requisitos de ancho de banda fuera del chip. También permite un servicio temprano para datos de carga críticos. Lo logra retrasando temporalmente las tiendas que de otro modo habrían ocupado el bus de datos. Al acceder a la etiqueta de almacenamiento actual con los últimos datos almacenados en arrays de datos y etiquetas de caché separadas, la unidad de dirección permite operaciones consecutivas de carga y almacenamiento en cualquier orden.

- Cachés: Alpha 21064 tiene dos cachés principales integrados llamados I-Cache y D-Cache. El I-Cache es un caché de instrucciones de 8 KB, mientras que el D-Cache es un caché de datos de 8 KB. Se han utilizado celdas de memoria estática de acceso aleatorio (SRAM) de seis transistores para construir estos cachés. B-Cache era un caché secundario opcional con capacidades de 128 KB a 16 MB. El caché operaba de 12,5 a 66,67 MHz a 200 MHz. Los tres cachés están mapeados directamente, pero I-Cache y D-cache tienen un ciclo de línea de 32 bytes, mientras que B-Cache tiene un tamaño de línea de 128 bytes de forma predeterminada.

- Interfaz: La interfaz es extremadamente flexible para adaptarse a una variedad de diseños de sistemas. Aunque el chip funciona con una fuente de alimentación de 3,3 voltios, también puede interactuar con una fuente de alimentación de 5 voltios. La interfaz externa es un bus de datos de 128 bits. El ancho del bus de datos se puede configurar y no solo puede tener la interfaz externa original de 128 bits, sino también la interfaz externa de 64 bits.

- Fabricación: Los aprendizajes del EV3 ayudaron en la fabricación del EV4. El EV3 se fabricó utilizando el proceso CMOS-3 de 1,0 micrómetros de Digital. El Alpha 21064 se fabricó utilizando un proceso CMOS-4 de 0,75 micrómetros que tenía 3 niveles de interconexión de aluminio. Contenía 1,68 millones de transistores. Mide 13,9 mm por 16,8 mm, para un área de 233,52 mm2. El proceso CMOS-4S tenía un tamaño de característica de 0,675 micrómetros. Este proceso se usó más tarde para la fabricación en lugar del CMOS-4 normal, lo que ayudó a reducir el tamaño total del chip de 233,52 mm2 a 186 mm2.

- Versiones mejoradas: hubo un mayor desarrollo sobre el Alpha 21064 original y muchas versiones salieron más tarde. Alpha 21064A, Alpha 21066, Alpha 21066A, Alpha 21068, Alpha 21068A son la versión mejorada que salió.

Publicación traducida automáticamente

Artículo escrito por anshuman350 y traducido por Barcelona Geeks. The original can be accessed here. Licence: CCBY-SA