En el Sistema Operativo (Técnica de Gestión de Memoria: Paginación ), para cada proceso se creará una tabla de páginas, que contendrá Entrada de Tabla de Páginas (PTE) . Este PTE contendrá información como el número de cuadro (la dirección de la memoria principal a la que queremos referirnos) y algunos otros bits útiles (p. ej., bit válido/inválido, bit sucio, bit de protección, etc.). Esta entrada de la tabla de páginas (PTE) indicará en qué lugar de la memoria principal reside la página real.

Ahora la pregunta es dónde colocar la tabla de páginas, de modo que el tiempo total de acceso (o tiempo de referencia) sea menor.

Inicialmente, el problema era acceder rápidamente al contenido de la memoria principal en función de la dirección generada por la CPU (es decir , dirección lógica/virtual ). Inicialmente, algunas personas pensaron en usar registros para almacenar tablas de páginas, ya que son memorias de alta velocidad, por lo que el tiempo de acceso será menor.

La idea utilizada aquí es colocar las entradas de la tabla de páginas en registros, para cada solicitud generada desde la CPU (dirección virtual), se comparará con el número de página apropiado de la tabla de páginas, que ahora indicará en qué parte de la memoria principal se encuentra la correspondiente. reside la página. Todo parece correcto aquí, pero el problema es que el tamaño del registro es pequeño (en la práctica, puede acomodar un máximo de 0,5k a 1k entradas de la tabla de páginas) y el tamaño del proceso puede ser grande, por lo que la tabla de páginas requerida también será grande (digamos que esta página la tabla contiene 1 millón de entradas), por lo que es posible que los registros no contengan todos los PTE de la tabla de páginas. Así que este no es un enfoque práctico.

Para superar este problema de tamaño, toda la tabla de páginas se mantuvo en la memoria principal. pero el problema aquí es que se requieren dos referencias de memoria principal:

- Para encontrar el número de cuadro

- Para ir a la dirección especificada por el número de marco

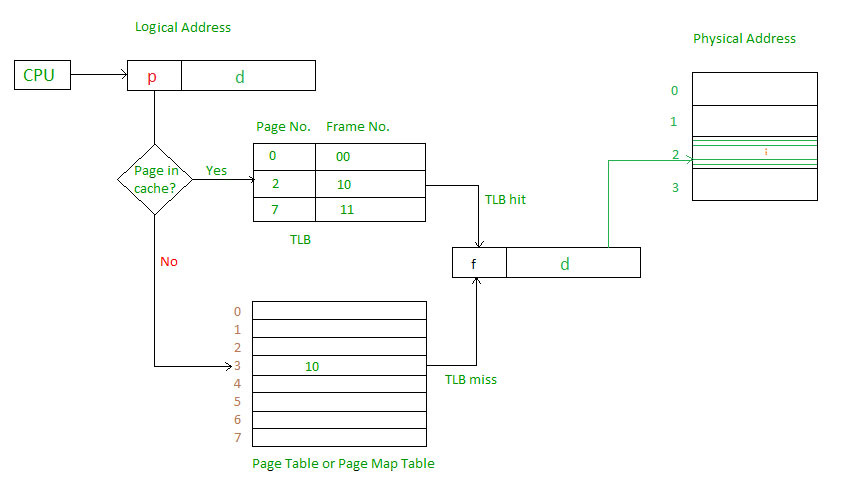

Para superar este problema, se configura una memoria caché de alta velocidad para las entradas de la tabla de páginas llamada Translation Lookaside Buffer (TLB). Translation Lookaside Buffer (TLB) no es más que un caché especial que se utiliza para realizar un seguimiento de las transacciones utilizadas recientemente. TLB contiene las entradas de la tabla de páginas que se han utilizado más recientemente. Dada una dirección virtual, el procesador examina el TLB si hay una entrada en la tabla de páginas (golpe de TLB), se recupera el número de trama y se forma la dirección real. Si una entrada de la tabla de páginas no se encuentra en el TLB (falta de TLB), el número de página se usa como índice mientras se procesa la tabla de páginas. TLB primero verifica si la página ya está en la memoria principal, si no está en la memoria principal, se emite una falla de página, entonces el TLB se actualiza para incluir la nueva entrada de página.

Pasos en TLB hit:

- La CPU genera una dirección virtual (lógica).

- Se comprueba en TLB (presente).

- Se recupera el número de fotograma correspondiente, que ahora indica dónde se encuentra la página de memoria principal.

Pasos en TLB miss:

- La CPU genera una dirección virtual (lógica).

- Se comprueba en TLB (no presente).

- Ahora el número de página coincide con la tabla de páginas que reside en la memoria principal (suponiendo que la tabla de páginas contiene todos los PTE).

- Se recupera el número de fotograma correspondiente, que ahora indica dónde se encuentra la página de memoria principal.

- El TLB se actualiza con un nuevo PTE (si no hay espacio, aparece una de las técnicas de reemplazo, es decir, FIFO, LRU o MFU, etc.).

Tiempo efectivo de acceso a la memoria (EMAT): TLB se utiliza para reducir el tiempo efectivo de acceso a la memoria, ya que es un caché asociativo de alta velocidad.

EMAT = h*(c+m) + (1-h)*(c+2m)

donde, h = proporción de aciertos de TLB

m = tiempo de acceso a la memoria

c = tiempo de acceso a TLB