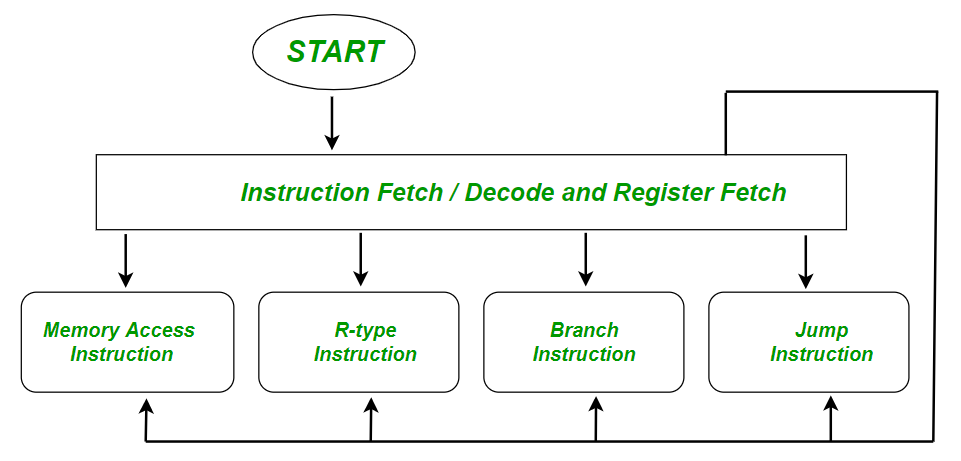

Descripción general :

La ruta de datos de ciclo múltiple divide las instrucciones en pasos separados. Reduce el tiempo medio de instrucción. Cada paso toma un solo ciclo de reloj. Cada unidad funcional se puede usar más de una vez en una instrucción, siempre que se use en diferentes ciclos de reloj. Reduce la cantidad de hardware necesario.

(I) Instrucción de obtención:

Una instrucción almacenada en la memoria se recupera en la unidad de control de la CPU proporcionando a la memoria la dirección de la respectiva instrucción dada.

- Supongamos que cada instrucción se almacena en una palabra y cada palabra tiene 4 bytes, por lo que podemos afirmar que la memoria es direccionable por bytes aquí.

- Sabemos que el Contador de programa (PC) contiene la dirección de la siguiente instrucción.

IR <= [[PC]] , PC <= [PC] + 4

(II) Decodificación (Instrucción de interpretación):

La unidad de control del procesador decodifica las instrucciones para encontrar la secuencia de operaciones requerida para ejecutar las instrucciones respectivas.

- Lectura del código de operación para determinar el tipo de instrucciones y la longitud del campo.

- Luego, lea los datos de todos los registros necesarios.

Ejemplo:

A <= Registro [IR [25:21]]; // Registrar rs en el código de operación (parte de la instrucción)

B <= Registro [IR [25:21]]; // Registrar rt en opcode (parte de la instrucción)

(III) Ejecución, Cómputo de Dirección de Memoria o Instrucción de Rama:

Ejemplos:

Memory Reference : ALUout <= A + sign-extend ( IR[15:0] ) Branch : if (A == B) PC <= ALUout // Conditional , it will calculate PC= Register + Branch Address Jump : PC <= PC [ 31:28 ] . ( IR [25 : 0] << 2 ) //// unconditional

(IV) Paso de finalización de instrucción de acceso a memoria/tipo R:

Ejemplos:

Memory Reference: MDR <= Memory [ALUout ]; // LOAD or Memory [ALUout ] <= B; // Store from register to memory Arithmetic Logic Instruction (R-type) : Reg [ IR[15:11]] <= ALUout ; // register destination in opcode

(V) Paso de finalización de lectura de memoria (escritura de registro):

- La mayoría de las instrucciones escriben el resultado de algún cálculo en un registro.

- Ejemplo: aritmética, lógica, turnos, cargas, etc. LOAD: Reg [ IR [20:16]] <= MDR

- Tiendas, sucursales, saltos no escriben en el registro al final y quedan ociosos.

Ejemplos:

Q1. Encuentre las etapas de ruta de datos y control (secuencia de ejecución) para

ADD R1, R2, R3;

significa R3 <– R1 + R2

Solución: Instrucción dada: AGREGAR R3, R1, R2;

- Etapa 1: Obtenga la instrucción y aumente el contador del programa.

- Etapa 2: Decodificar para determinar que es una instrucción ADD y leer los registros R1 y R2.

- Etapa 3: Sume los dos valores respectivos recuperados en la Etapa 2.

- Etapa 4: inactivo (nada que escribir en la memoria)

- Etapa 5: Escriba el resultado de la Etapa 3 en el registro R3.

Q2. Encuentre las etapas de ruta de datos y control (secuencia de ejecución) para

MOV 30 (R1), R2;

significa [30 + R1] <– R2

Solución: Instrucción dada – MOV 30 (R1), R2;

- Etapa 1 (Fetch): Obtener la instrucción y aumentar el contador del programa.

- Etapa 2 (Decodificación): Decodificar para encontrar la instrucción respectiva es MOV y leer los registros R1 y R2

- Etapa 3 (Ejecutar): Agregar 30 al valor en el respectivo registro R1.

- Etapa 4 (Acceso a la memoria): Escriba el valor en el registro R2 en la dirección de memoria calculada en la Etapa 3.

- Etapa 5 (Escritura de registro): este paso está inactivo (no hay nada que escribir en el registro)

Publicación traducida automáticamente

Artículo escrito por infoutkarsh y traducido por Barcelona Geeks. The original can be accessed here. Licence: CCBY-SA