Tanto CPU Cache como TLB son hardware utilizado en microprocesadores, pero ¿cuál es la diferencia, especialmente cuando alguien dice que TLB también es un tipo de caché?

Primero lo primero. caché de la CPUes una memoria rápida que se utiliza para mejorar la latencia de obtener información de la memoria principal (RAM) a los registros de la CPU. Entonces CPU Cache se encuentra entre la memoria principal y la CPU. Y este caché almacena información temporalmente para que el próximo acceso a la misma información sea más rápido. Un caché de CPU que solía almacenar instrucciones ejecutables, se llama Caché de instrucciones (I-Cache). Un caché de CPU se utiliza para almacenar datos, se llama caché de datos (D-Cache). Por lo tanto, I-Cache y D-cache aceleran el tiempo de obtención de instrucciones y datos, respectivamente. Un procesador moderno contiene I-Cache y D-Cache. Para completar, analicemos también la jerarquía de caché D. D-Cache generalmente se organiza en una jerarquía, es decir, caché de datos de nivel 1, caché de datos de nivel 2, etc. Debe tenerse en cuenta que L1 D-cache es más rápido/más pequeño/más costoso en comparación con L2 D-Cache. Pero la idea básica de ‘El caché de la CPU es para acelerar el tiempo de obtención de instrucciones/datos desde la memoria principal a la CPU.

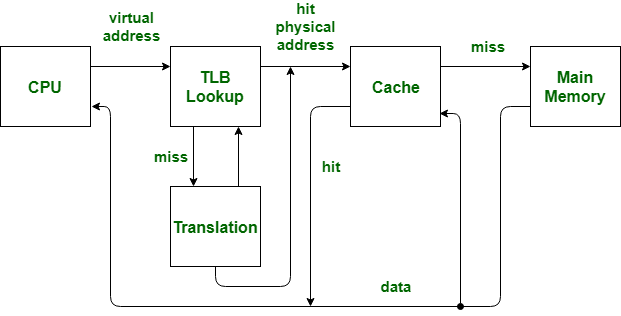

Translation Lookaside Buffer (es decir, TLB) solo se requiere si un procesador utiliza la memoria virtual. En resumen, TLB acelera la traducción de direcciones virtuales a una dirección física al almacenar la tabla de páginas en una memoria más rápida. De hecho, TLB también se encuentra entre la CPU y la memoria principal. Precisamente hablando, MMU utiliza TLB cuando una dirección virtual necesita traducirse a una dirección física. Al mantener este mapeo de direcciones físicas virtuales en memoria rápida, mejora el acceso a la tabla de páginas. Cabe señalar que la tabla de páginas (que a su vez se almacena en la RAM) realiza un seguimiento de dónde se almacenan las páginas virtuales en la memoria física. En ese sentido, TLB también puede considerarse como un caché de la tabla de páginas.

Pero el alcance de la operación para TLB y CPU Cach e es diferente. TLB se trata de ‘acelerar la traducción de direcciones para la memoria virtual’, por lo que no es necesario acceder a la tabla de páginas para cada dirección. CPU Cache se trata de ‘acelerar la latencia de acceso a la memoria principal’ para que la CPU no acceda siempre a la RAM. La operación TLB se produce en el momento de la traducción de direcciones por parte de MMU, mientras que la operación de caché de la CPU se produce en el momento del acceso a la memoria por parte de la CPU. De hecho, cualquier procesador moderno implementa todo I-Cache, L1 y L2 D-Cache y TLB.

Entendamos esto en forma tabular:

| caché de la CPU | TLB | |

| 1. | Caché de la CPU significa caché de la unidad central de procesamiento | TLB significa Translation Lookaside Buffer |

| 2. | El caché de la CPU es un caché de hardware | Es un caché de memoria que almacena traducciones recientes de memoria virtual a memoria física en la computadora. |

| 3. | Se utiliza para reducir el tiempo medio de acceso a los datos de la memoria principal. | Se utiliza para reducir el tiempo que tarda un usuario en acceder a la ubicación de la memoria desde la memoria principal de nuestra computadora. |

| 4. | Almacena copias de los datos de las ubicaciones de la memoria principal que se utilizan con frecuencia porque se encuentra más cerca del núcleo del procesador. | La mayoría de nuestras computadoras incluyen más de 1 TLB en MMH (hardware de administración de memoria) |

| 5. | Ejemplo: caché L1, caché L2, caché L3 | Ejemplo -: L1 TLB |

Haga clic en Me gusta/Compartir si encuentra útil lo anterior. Además, déjenos un comentario para obtener más aclaraciones o información. Nos encantaría ayudar y aprender 🙂

Publicación traducida automáticamente

Artículo escrito por GeeksforGeeks-1 y traducido por Barcelona Geeks. The original can be accessed here. Licence: CCBY-SA