El procesador 8086 proporciona un bus de datos de 16 bits. Entonces, es capaz de transferir 16 bits en un ciclo, pero cada ubicación de memoria es solo de un byte (8 bits), por lo tanto, necesitamos dos ciclos para acceder a 16 bits (8 bits cada uno) desde dos ubicaciones de memoria diferentes. La solución a este problema es el Banco de Memoria. A través del banco de memoria, nuestro objetivo es acceder a dos ubicaciones de memoria consecutivas en un ciclo (transferir 16 bits).

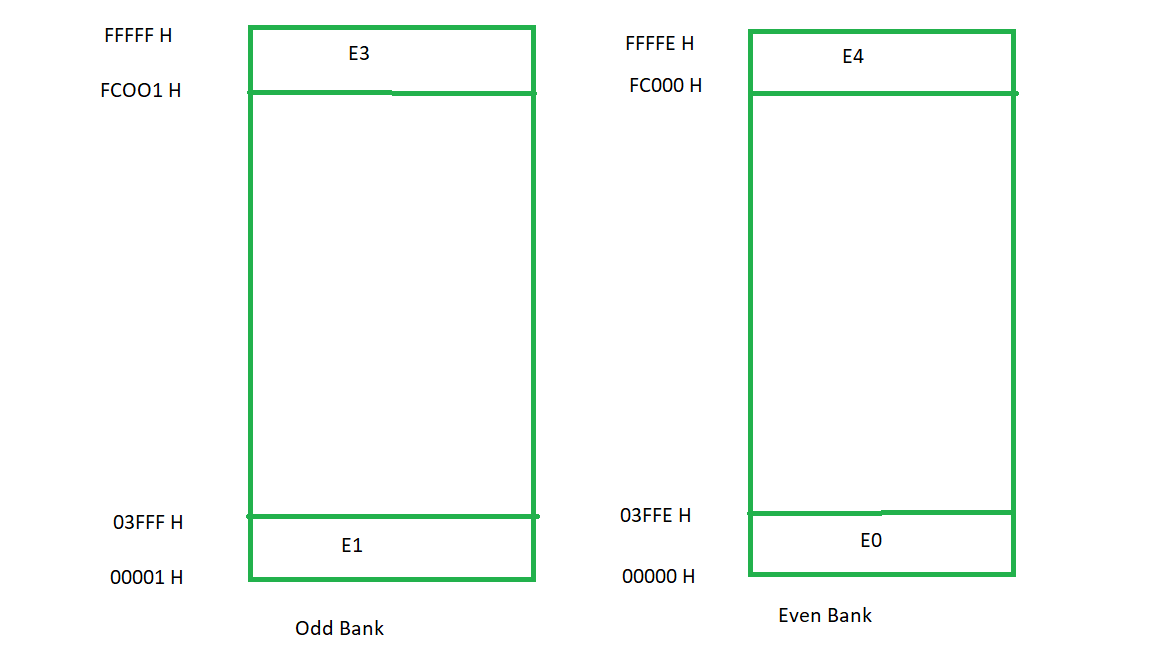

El chip de memoria se divide igualmente en dos partes (bancos). Uno de los bancos contiene direcciones pares denominadas banco par y el otro contiene direcciones impares denominadas banco impar . El banco par siempre proporciona un byte más bajo. Por lo tanto, el banco par también se denomina banco inferior (LB) y el banco impar también se denomina banco superior (HB).

Este esquema bancario permite acceder a dos ubicaciones de memoria alineadas desde ambos bancos simultáneamente y procesar la transferencia de datos de 16 bits. El banco de memoria no obliga a transferir 16 bits, facilita la transferencia de datos de 16 bits.

La elección entre la transferencia de 8 y 16 bits depende de las instrucciones dadas por el programador.

Ejemplo:

El bit menos significativo de la dirección (A 0 no se usa para la selección de bytes) está reservado para la selección de bancos. Por lo tanto, A 0 = 0 seleccionará el banco par. La señal BHE se utiliza para la selección de bancos impares. El procesador utilizará una combinación de estas dos señales para decidir el tipo de transferencia de datos.

| BHE | un 0 | tipos de Transferencia |

|---|---|---|

| 0 | 0 | Transferencia de datos de 16 bits desde HB y LB |

| 0 | 1 | Transferencia de datos de 8 bits desde HB |

| 1 | 0 | transferencia de datos de 8 bits desde LB |

| 1 | 1 | Ninguno (inactivo) |

En este caso, el primer ciclo de la máquina genera una dirección impar (A 0 = 1) y transfiere 8 bits de datos de orden inferior en un bus de datos de orden superior. En el segundo ciclo de la máquina, el bus de datos de orden superior se transferirá al bus de datos de orden inferior.

Publicación traducida automáticamente

Artículo escrito por sonalilotankar y traducido por Barcelona Geeks. The original can be accessed here. Licence: CCBY-SA