¿Qué es el decrementador binario de 4 bits?

Resta 1 valor binario del valor binario existente almacenado en el registro o, en otras palabras, simplemente podemos decir que disminuye el valor existente almacenado en el registro en 1.

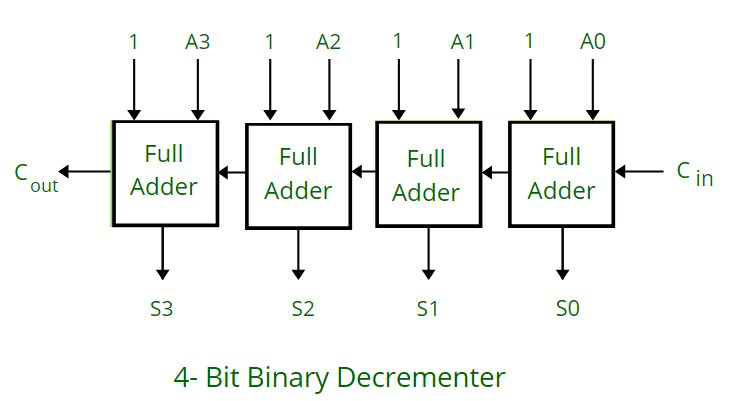

Para cualquier decrementador binario de n bits, ‘n’ se refiere al almacenamiento capacidad del registro que debe disminuirse en 1. Por lo tanto, requerimos ‘n’ número de sumadores completos. Por lo tanto, en el caso de un decrementador binario de 4 bits, necesitamos 4 sumadores completos.

Laboral:

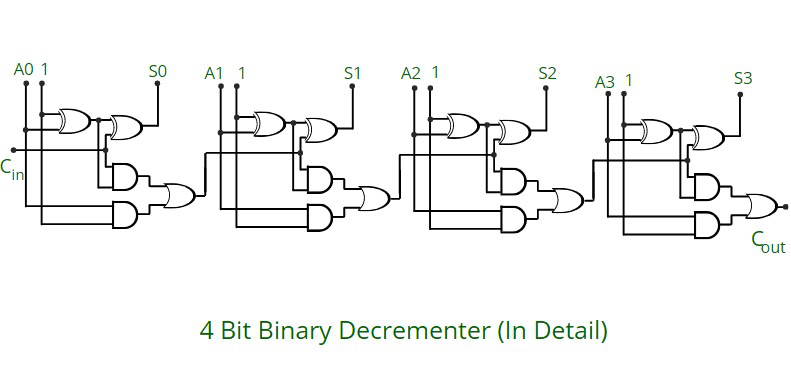

- Consta de 4 sumadores completos, conectados uno tras otro. Cada sumador completo tiene 3 entradas (entrada de acarreo, 1, A) y 2 salidas (salida de acarreo y S)

- Un sumador completo básico consta de 2 medios sumadores y una puerta OR.

- El acarreo (C) del sumador completo anterior se propaga al siguiente sumador completo. Entonces, la salida de acarreo de un sumador completo se convierte en una de las tres entradas del siguiente sumador completo.

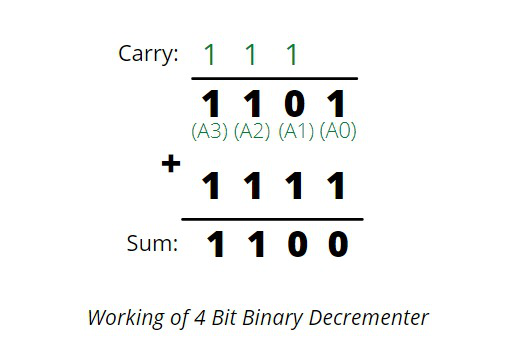

- Sigue el concepto de complemento a 2, por lo que tomamos 1 como entrada en los 4 sumadores completos como se ve en el diagrama anterior.

- Entonces sumamos 1111 para restar 1.

Razón para agregar 1111:

- Esto se debe a que nuestro motivo principal es restar 1, que en representación de 4 bits es 0001

- Representarlo en complemento a 1 dará: 1110

- Representarlo en complemento a 2 (sumando 1 al complemento a 1) dará: 1111

- Esta es la razón por la que se proporciona la entrada 1111 para obtener una salida decrementada en un decrementador binario de 4 bits.

In 4 bit representation In 1's complement In 2's complement

1 -------------------------> 0001 ----------------------> 1110 ---------------------> 1111

Ejemplo:

(Refer to the circuit diagram from right to left for better understanding)

1. Input: 1010 ----> After using 4 bit binary decrementer ----> Output: 1001

1 0 1 0 (Comparing from the circuit 1 0 1 0 is A3, A2, A1, A0 respectively)

+ 1 1 1 1 (1 1 1 1 is added as seen in the diagram also, in each full adder 1 is taken as input)

________

1 0 1 1 ( 1 0 1 1 , in the diagram are S3, S2, S1, S0 respectively)

________

2. Input: 0010 ----> After using 4 bit binary decrementer ----> Output: 0001 1 0 1 0 + 1 1 1 1 ________ 0 0 0 1 ________

3. Input: 0011 ----> After using 4 bit binary decrementer ----> Output: 0001 0 0 1 1 + 1 1 1 1 _________ 0 0 1 0 _________

Publicación traducida automáticamente

Artículo escrito por tausifsiddiqui y traducido por Barcelona Geeks. The original can be accessed here. Licence: CCBY-SA