Prerrequisito: Estudio detallado de la estructura de interconexión de Time Shared Bus , Crossbar Switch y Multiport Memory .

Introducción:

la estructura de interconexión puede decidir el rendimiento general del sistema en un entorno multiprocesador. Los procesadores deben poder compartir un conjunto de módulos de memoria principal y dispositivos de E/S en un sistema multiprocesador. Esta capacidad de compartición puede proporcionarse a través de estructuras de interconexión. La estructura de interconexión que se usa comúnmente se puede dar de la siguiente manera:

- Tiempo compartido / Bus común (discutido anteriormente)

- Interruptor de barra transversal

- Memoria multipuerto

- Red de conmutación multietapa (discutido anteriormente)

Tiempo compartido / Bus común:

en un sistema multiprocesador, la interconexión del bus de tiempo compartido proporciona una ruta de comunicación común que conecta todas las unidades funcionales.

Tiempo Compartido/Bus Común en Sistema Multiprocesador

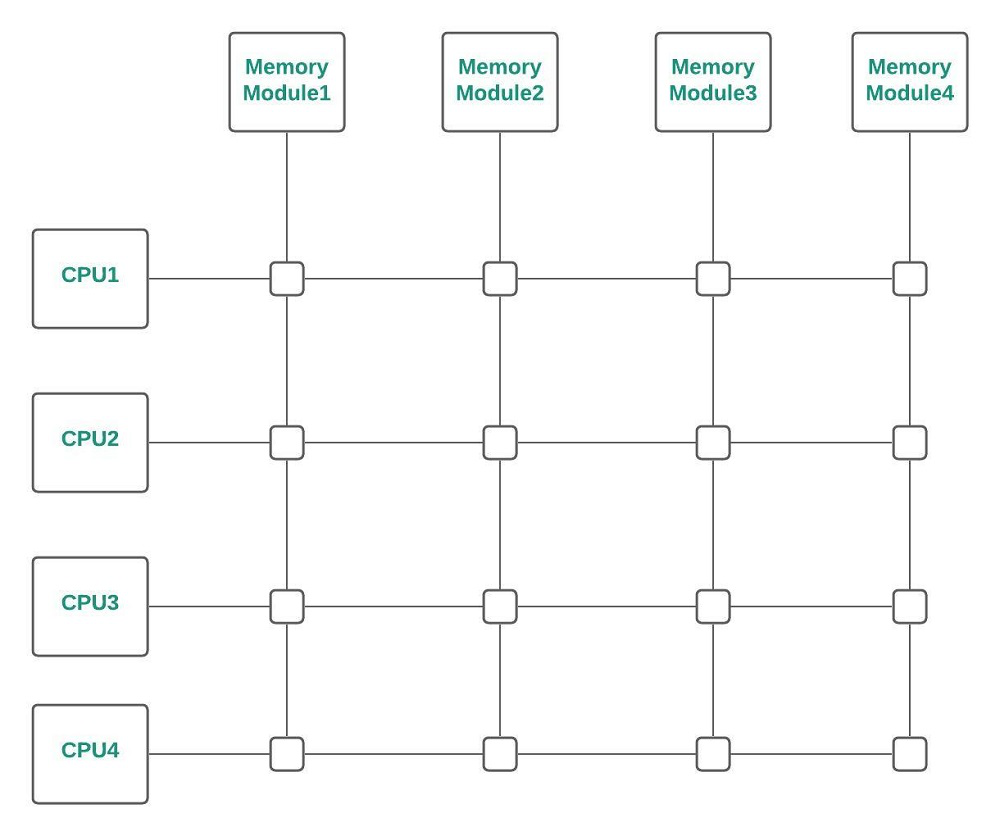

Interruptor de barra transversal:

se llega a un punto en el que hay una ruta separada disponible para cada módulo de memoria, si se aumenta el número de buses en el sistema de bus común. Crossbar Switch (para multiprocesadores) proporciona una ruta separada para cada módulo.

Interruptor de barra transversal

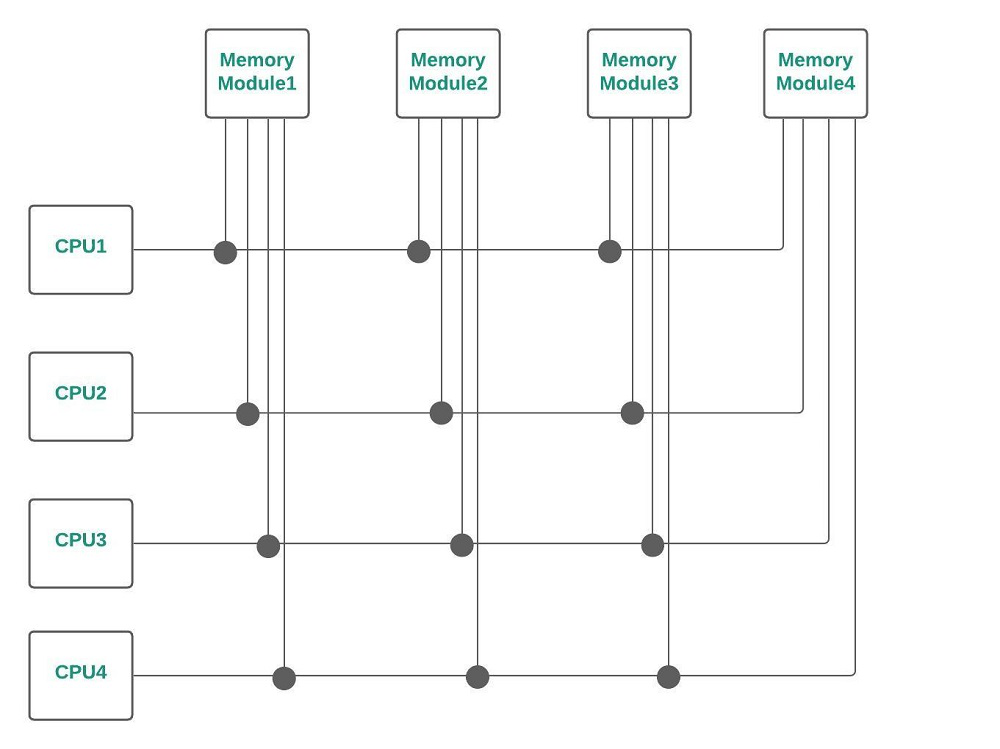

Memoria multipuerto:

en los sistemas de memoria multipuerto, la lógica de control, conmutación y arbitraje de prioridad se distribuye a través de la array de interruptores de barra transversal que se distribuye en las interfaces a los módulos de memoria.

Memoria multipuerto

Diferencia entre bus de tiempo compartido, conmutador de barra transversal y memoria multipuerto:

| Autobús de tiempo compartido | Interruptor de barra transversal | Memoria multipuerto | |

| 1. | El costo más bajo para hardware y menos complejo. | Rentable para multiprocesadores solo porque se requiere una array de conmutación básica (para ensamblar unidades funcionales). | Como la mayoría de los circuitos de control y conmutación están en la unidad de memoria, es costoso. |

| 2. | La expansión del sistema degradará el rendimiento. | La expansión del sistema puede mejorar el rendimiento. | Es difícil ampliar el sistema (diseño). |

| 3. | En general, la capacidad del sistema limita la tasa de transferencia y si el bus falla, todo el sistema fallará. | La tasa de transferencia es alta pero más compleja. | Potencial para una tasa de transferencia total muy alta. |

| 4. | Modificar la configuración del sistema de hardware es fácil. | Expansión limitada del sistema, solo por el tamaño de la array de interruptores. | Se requieren muchos cables y conectores. |

| 5. | No podemos tener transferencias desde todos los módulos de memoria simultáneamente. | Podemos tener transferencias desde todos los módulos de memoria simultáneamente. | Podemos tener transferencias desde todos los módulos de memoria simultáneamente. |

| 6. | Mínima eficiencia y adecuado solo para sistemas más pequeños. | Las unidades funcionales son las más sencillas y baratas. | Las unidades funcionales permiten un monoprocesador de bajo costo. |

Publicación traducida automáticamente

Artículo escrito por sameekshakhandelwal1712 y traducido por Barcelona Geeks. The original can be accessed here. Licence: CCBY-SA