Este artículo trata sobre una técnica de decodificación que utiliza el 74139 , un decodificador de 2 a 4.

El dispositivo mencionado anteriormente tiene dos decodificadores de 2 a 4 en el interior, uno se usa para conectar los puertos de E/S y el segundo se usa para conectar la memoria.

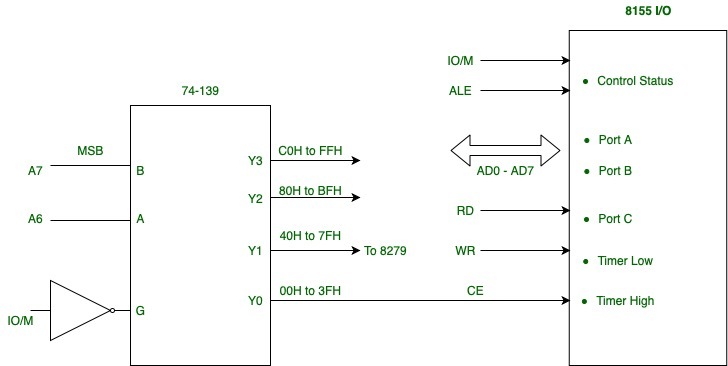

Veamos la interfaz de E/S:

- La entrada al decodificador son las líneas de dirección A7 y A6.

- El decodificador es habilitado por la señal IO/M a través de un inversor.

- Cada vez que el procesador afirma que IO/M es alto para acceder a un puerto de E/S, el decodificador se activa.

- Las líneas de dirección A5-A0 no están decodificadas en este esquema, algunas de ellas están conectadas a dispositivos de E/S programables como el 8155 y el 8279

La figura se verá algo como esto:

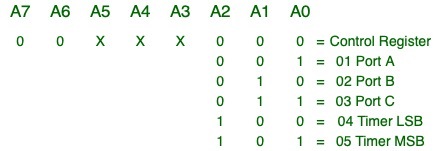

8155 Direcciones de E/S:

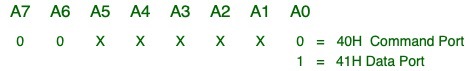

8279 Direcciones de E/S:

Múltiples direcciones de E/S:

El 8279 solo necesita dos direcciones, pero debido a las cinco líneas indiferentes, ocupa el espacio de 64 direcciones de E/S. En el caso del 8155 , tres líneas de direcciones no importan; por lo tanto, tiene ocho conjuntos de rangos de direcciones para sus puertos de E/S y el temporizador.

ventajas:

- Ahorre costos

- Ahorra espacio