Requisito previo: canalización

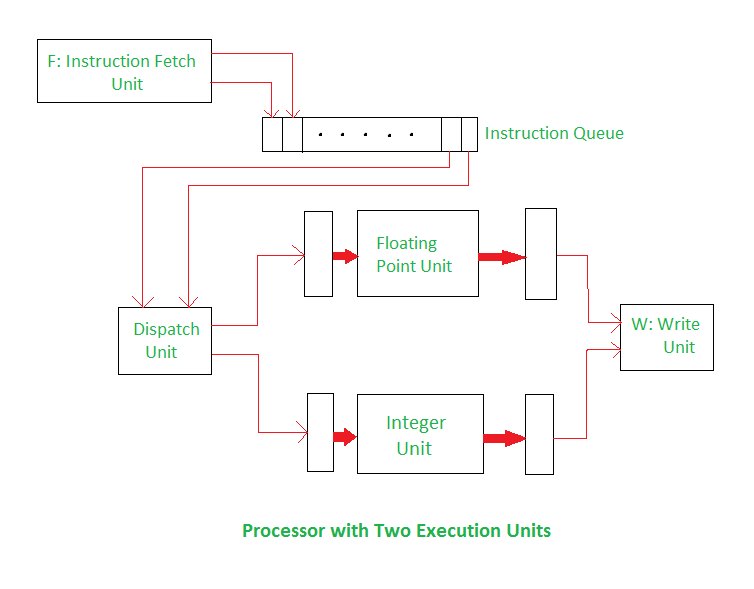

Un enfoque más agresivo consiste en equipar el procesador con varias unidades de procesamiento para manejar varias instrucciones en paralelo en cada etapa de procesamiento. Con este arreglo, varias instrucciones comienzan a ejecutarse en el mismo ciclo de reloj y se dice que el proceso usa problemas múltiples. Dichos procesadores son capaces de lograr un rendimiento de ejecución de instrucciones de más de una instrucción por ciclo. Son conocidos como ‘Procesadores Superescalares’.

En el diagrama anterior, hay un procesador con dos unidades de ejecución; uno para enteros y otro para operaciones de punto flotante. La unidad de búsqueda de instrucciones es capaz de leer las instrucciones a la vez y almacenarlas en la cola de instrucciones. En cada ciclo, la unidad de despacho recupera y decodifica hasta dos instrucciones del frente de la cola. Si hay un número entero, una instrucción de punto flotante y ningún peligro, ambas instrucciones se envían en el mismo ciclo de reloj.

Ventajas de la arquitectura superescalar:

- El compilador puede evitar muchos peligros mediante una selección y un orden juiciosos de las instrucciones.

- El compilador debe esforzarse por intercalar instrucciones de punto flotante y entero. Esto permitiría que la unidad de despacho mantuviera ocupadas tanto la unidad de enteros como la de punto flotante la mayor parte del tiempo.

- En general, se logra un alto rendimiento si el compilador puede organizar las instrucciones del programa para aprovechar al máximo las unidades de hardware disponibles.

Desventajas de la arquitectura superescalar:

- En un procesador superescalar, el efecto perjudicial sobre el rendimiento de varios peligros se vuelve aún más pronunciado.

- Debido a este tipo de arquitectura, pueden ocurrir problemas en la programación.

Publicación traducida automáticamente

Artículo escrito por akankshasadvelkar y traducido por Barcelona Geeks. The original can be accessed here. Licence: CCBY-SA