Requisito previo: tipos de flip-flop y su conversión

Condición de carrera en el flip-flop JK: para el flip-flop JK, si J = K = 1, y si clk = 1 durante un largo período de tiempo, la salida Q alternará siempre que CLK sea alto, lo que hace que la salida del flip-flop inestable o incierto. Este problema se denomina condición de carrera en el flip-flop JK. Este problema (condición de carrera alrededor) se puede evitar asegurándose de que la entrada del reloj esté en la lógica «1» solo por un tiempo muy corto. Esto introdujo el concepto de flip flop Master Slave JK .

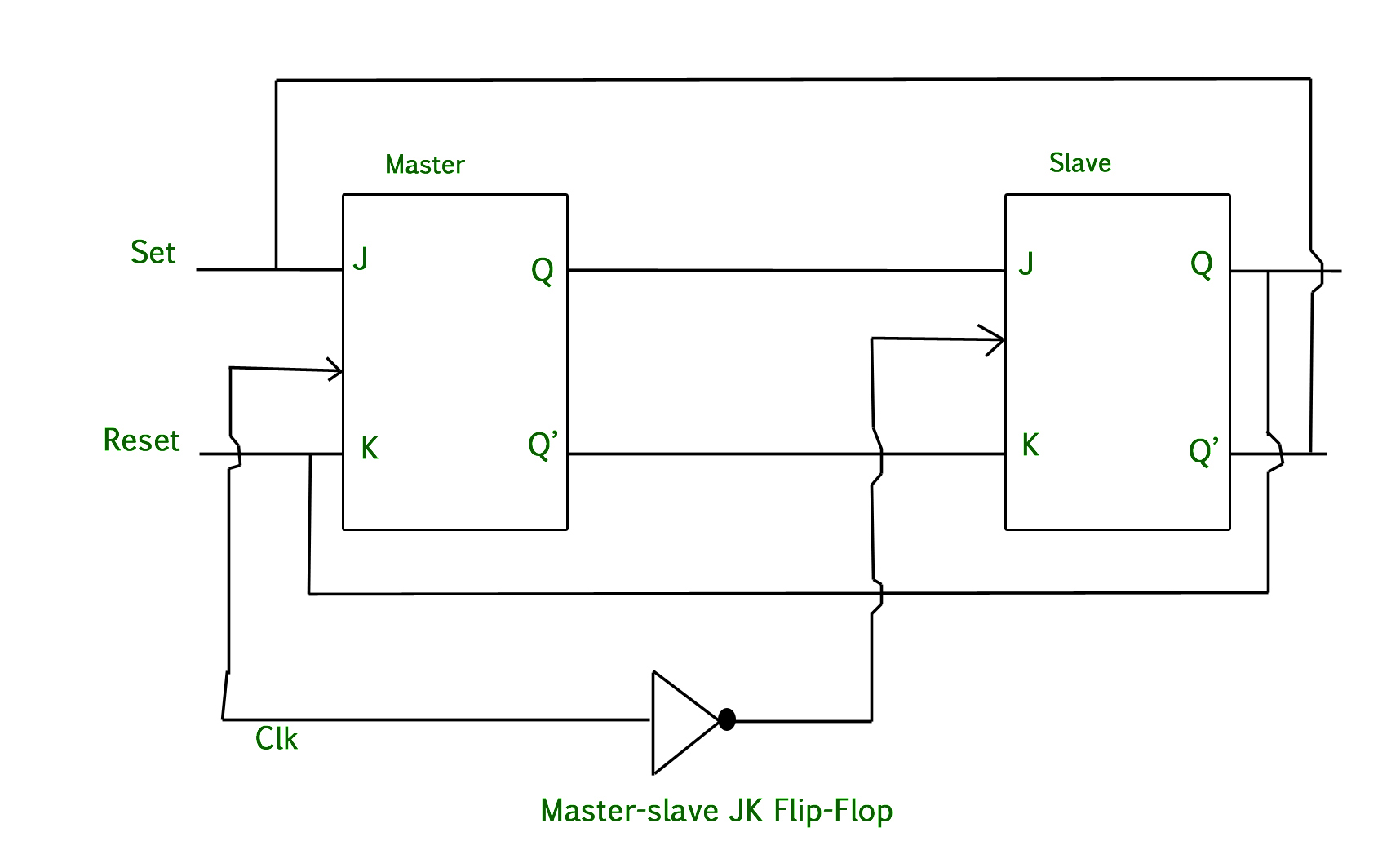

Flip flop Master Slave JK:

el flip-flop Master-Slave es básicamente una combinación de dos flip-flops JK conectados entre sí en una configuración en serie. De estos, uno actúa como “amo” y el otro como “esclavo” . La salida del flip flop maestro se conecta a las dos entradas del flip flop esclavo, cuya salida se retroalimenta a las entradas del flip flop maestro.

Además de estos dos flip-flops, el circuito también incluye un inversor . El inversor está conectado al pulso de reloj de tal manera que el pulso de reloj invertido se entrega al flip-flop esclavo. En otras palabras, si CP=0 para un flip-flop maestro, entonces CP=1 para un flip-flop esclavo y si CP=1 para un flip-flop maestro, se convierte en 0 para un flip-flop esclavo.

Funcionamiento de un flip flop maestro esclavo –

- Cuando el pulso del reloj va a 1, el esclavo se aísla; Las entradas J y K pueden afectar el estado del sistema. El flip-flop esclavo está aislado hasta que el CP pasa a 0. Cuando el CP vuelve a 0, la información pasa del flip-flop maestro al esclavo y se obtiene la salida.

- En primer lugar, el flip flop maestro se activa en nivel positivo y el flip flop esclavo se activa en nivel negativo, por lo que el maestro responde antes que el esclavo.

- Si J=0 y K=1, la salida Q’ alta del maestro va a la entrada K del esclavo y el reloj obliga al esclavo a reiniciarse, por lo que el esclavo copia al maestro.

- Si J=1 y K=0, la salida Q alta del maestro va a la entrada J del esclavo y la transición Negativa del reloj establece el esclavo, copiando al maestro.

- Si J=1 y K=1, cambia a la transición positiva del reloj y, por lo tanto, el esclavo cambia a la transición negativa del reloj.

- Si J=0 y K=0, el flip flop se desactiva y Q permanece sin cambios.

Diagrama de tiempo de un flip flop maestro:

- Cuando el pulso del reloj es alto, la salida del maestro es alta y permanece alta hasta que el reloj es bajo porque el estado se almacena.

- Ahora, la salida del maestro se vuelve baja cuando el pulso del reloj vuelve a ser alto y permanece baja hasta que el reloj vuelve a ser alto.

- Por lo tanto, la alternancia tiene lugar durante un ciclo de reloj.

- Cuando el pulso del reloj es alto, el maestro está operativo pero no el esclavo, por lo que la salida del esclavo permanece baja hasta que el reloj permanece alto.

- Cuando el reloj está bajo, el esclavo se vuelve operativo y permanece alto hasta que el reloj vuelve a estar bajo.

- La alternancia tiene lugar durante todo el proceso, ya que la salida cambia una vez en un ciclo.

Esto hace que el flip flop Master-Slave JK sea un dispositivo síncrono, ya que solo pasa datos con la sincronización de la señal del reloj.

Publicación traducida automáticamente

Artículo escrito por Harshita Pandey y traducido por Barcelona Geeks. The original can be accessed here. Licence: CCBY-SA