Requisito previo: introducción de puertas lógicas

Diseñar e implementar las puertas lógicas AND y OR utilizando el lenguaje de programación VHDL (Lenguaje de descripción de hardware VHSIC).

Diferentes tipos de estilos de modelado VHDL

La arquitectura del código VHDL está escrita en tres estilos de codificación diferentes:

- Modelado de flujo de datos

- Modelado de comportamiento

- Modelado Estructural

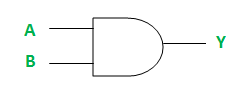

1. Desarrollo lógico para la puerta AND: La puerta lógica AND se puede realizar de la siguiente manera:

La tabla de verdad de AND Gate es:

| A | B | Y = A Y B |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Implementación del modelado de flujo de datos: a continuación se muestra la implementación de la lógica anterior en el lenguaje VHDL (modelado de flujo de datos).

-- VHDL Code for AND gate

-- Header file declaration

library IEEE;

use IEEE.std_logic_1164.all;

-- Entity declaration

entity andGate is

port(A : in std_logic; -- AND gate input

B : in std_logic; -- AND gate input

Y : out std_logic); -- AND gate output

end andGate;

-- Dataflow Modelling Style

-- Architecture definition

architecture andLogic of andGate is

begin

Y <= A AND B;

end andLogic;

2. Desarrollo lógico para la puerta OR: la puerta lógica OR se puede realizar de la siguiente manera:

La tabla de verdad para OR Gate es:

| A | B | Y = A O B |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Implementación del modelado de flujo de datos: a continuación se muestra la implementación de la lógica anterior en el lenguaje VHDL (modelado de flujo de datos).

-- VHDL Code for OR gate

-- Header file declaration

library IEEE;

use IEEE.std_logic_1164.all;

-- Entity declaration

entity orGate is

port(A : in std_logic; -- OR gate input

B : in std_logic; -- OR gate input

Y : out std_logic); -- OR gate output

end orGate;

-- Dataflow Modelling Style

-- Architecture definition

architecture orLogic of orGate is

begin

Y <= A OR B;

end orLogic;

Publicación traducida automáticamente

Artículo escrito por PratikBasu y traducido por Barcelona Geeks. The original can be accessed here. Licence: CCBY-SA