Flip-Flop se conoce popularmente como el circuito básico de memoria digital. Tiene dos estados como 1 lógico (alto) y 0 lógico (bajo). Un flip flop es un circuito secuencial que consta de un solo estado binario de información o datos. El circuito digital es un flip flop que tiene dos salidas y son de estados opuestos. También se le conoce como Multivibrador Biestable.

1. Flip Flop JK:

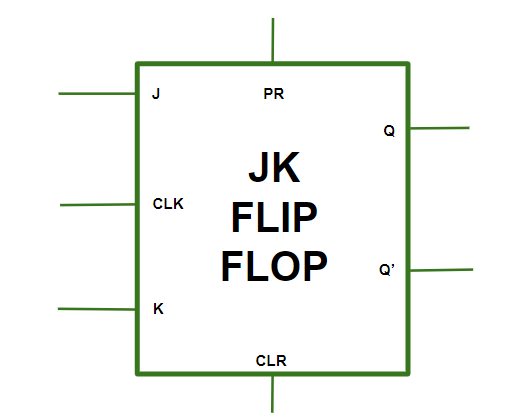

El siguiente diagrama de flip flop JK representa la estructura básica que consta de Reloj (CLK), Clear (CLR) y Preset (PR).

Operaciones en JK Flip-Flop –

- Caso 1:

PR = CLR = 0

Esta condición está en su estado inválido.

- Caso-2:

PR = 0 and CLR = 1

El PR está activado, lo que significa que la salida en Q se establece en 1. Por lo tanto, el flip flop está en el estado establecido.

- Caso-3:

PR = 1 and CLR = 0

El CLR está activado, lo que significa que la salida en Q’ se establece en 1. Por lo tanto, el flip flop está en estado de reinicio.

- Caso-4:

PR = CLR = 1

En esta condición, el flip flop funciona normalmente mientras que PR y CLR se desactivan.

JK Flip-Flop con la representación de Preset y Clear –

Tabla de verdad para JK Flip-Flop –

Race Around Condition en JK Flip-Flop:

cuando tanto J como K se establecen en 1, la entrada permanece alta durante más tiempo y luego la salida sigue alternando. Alternar significa cambiar la salida instantáneamente, es decir, Q = 0, Q’ = 1 cambiará inmediatamente a Q = 1 y Q’ = 0 y esta continuación sigue cambiando. Este cambio en la salida conduce a la Condición de carrera alrededor.

2. Flip-Flop

SR: En el flip-flop SR, con la ayuda de Preset y Clear, cuando se enciende la alimentación, el estado del circuito sigue cambiando, es decir, es incierto. Puede llegar al estado Set (Q = 1) o Reset (Q’ = 0). En muchas aplicaciones, se desea configurar o restablecer inicialmente el flip flop. Esto se logra con Preset (PR) y Clear (CLR).

Operaciones en SR Flip-Flop –

- Caso 1:

PR = CLR = 1

Las entradas asíncronas están inactivas y el flip flop responde libremente a las entradas S, R y CLK de forma normal.

- Caso-2:

PR = 0 and CLR = 1

Esto se usa cuando Q se establece en 1.

- Caso-3:

PR = 1 and CLR = 0

Esto se usa cuando Q’ se establece en 1.

- Caso-4:

PR = CLR = 0

Este es un estado inválido.

SR Flip-Flop con la representación de Preset y Clear –

Tabla de verdad para SR Flip-Flop –

Aplicaciones de Flip-Flop:

- Los flip-flops se utilizan como un interruptor de eliminación de rebotes.

- Se utilizan como conversión de serie a paralelo y de paralelo a serie.

- Se utiliza para mostradores.

- Se utiliza para divisor de frecuencia y también como cerrojo.

Publicación traducida automáticamente

Artículo escrito por sakshiparikh23 y traducido por Barcelona Geeks. The original can be accessed here. Licence: CCBY-SA