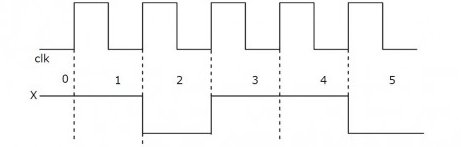

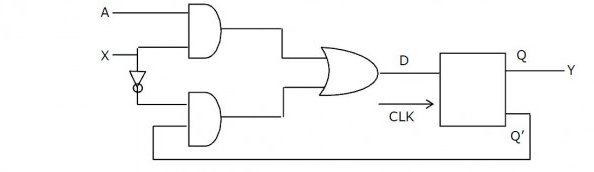

Considere el siguiente circuito que involucra un flanco positivo disparado D FF. Considere el siguiente diagrama de tiempo. Sea Ai el nivel lógico en la línea A en el i-ésimo período de reloj.

Sea A’ el complemento de A. La secuencia de salida correcta en Y durante los períodos de reloj del 1 al 5 es

(A) A0 Al A1′ A3 A4

(B) A0 Al A2′ A3 A4

(C) Al A2 A2′ A3 A4

(D) Al A2′ A3 A4 A5′

Respuesta: (A)

Explicación: El flip flop que se usa aquí es un flip flop D activado por flanco positivo, lo que significa que solo en el » flanco ascendente del reloj » el flip flop capturará la entrada proporcionado en D y, en consecuencia, da la salida en Q. Y en otros momentos del reloj, la salida no cambia. La salida del flip flop D es la misma que la entrada, es decir, Y=Q=D (en el flanco ascendente).

Ahora, en la pregunta anterior, se dan 5 períodos de reloj y tenemos que encontrar la salida Q o Y en esos períodos de reloj.

Primero, obtengamos la expresión booleana para la puerta lógica.

que es:

D = AX + X’ Q’

Ahora,

En el primer período de reloj , (es decir, cuando t = 0 a 1)

aquí el reloj tiene un borde ascendente en t = 0, por lo tanto, solo en este momento, el flip flop D cambiará su estado.

En el primer reloj, X = 1, entonces, D = A. Ahora, una línea lógica puede tener diferentes niveles en diferentes períodos de reloj, es decir, puede ser alto o bajo, por lo tanto, tenemos que responder con respecto al i-ésimo período de reloj donde Ai es el nivel lógico (alto o bajo) de la línea lógica A en el i-ésimo reloj.

Entonces, en el primer período de reloj, el valor lógico de A debe ser A1 (es decir, el valor de A en el primer período de reloj), pero debido al retraso proporcionado por las puertas lógicas (retardo de propagación) , el valor de A utilizado por Flip Flop es el valor anterior de A solamente, es decir, capturará el valor de D resultante al usar la línea lógica A en el período de reloj 0, que es A0. Lo mismo ocurre con el valor de X, es decir, en lugar de Xi, se utiliza el valor anterior de X en el i-ésimo período de reloj, que es Xi-1.

Ahora, en el primer período de reloj, el valor de X es el mismo que en el reloj 0, es decir, lógica 1. Entonces, X = 1 y A = A0, por lo tanto, D = A0 y, por lo tanto, Q = Y = A0

De manera similar, tenemos que hacer para otros períodos de reloj, es decir, en lugar de tomar Ai y Xi, se deben tomar Ai-1 y Xi-1 para obtener la salida en el i-ésimo período de reloj.

En el segundo período de reloj , (es decir, cuando t = 1 a 2)

X = 1 (valor en el reloj anterior), Entonces, D = A1 (valor de A en el reloj anterior), por lo tanto Q = Y = A1

En el tercer período de reloj , (es decir, cuando t = 2 a 3)

X = 0 (valor en el reloj anterior, vea el diagrama de tiempo), Entonces, D = Q’ = A1′, por lo tanto, Q = Y = A1′ (debido a la línea de retroalimentación)

En el cuarto período de reloj , (es decir, cuando t = 3 a 4)

X = 1 ( valor en el reloj anterior, ), Entonces, D = A3 , por lo tanto Q = Y = A3

En el quinto período de reloj , (es decir, cuando t = 4 a 5)

X = 1 (valor en el reloj anterior), entonces, D = A4, por lo tanto Q = Y = A4

Por lo tanto, la secuencia de salida es: A0 A1 A1′ A3 A4 .

Publicación traducida automáticamente

Artículo escrito por GeeksforGeeks-1 y traducido por Barcelona Geeks. The original can be accessed here. Licence: CCBY-SA