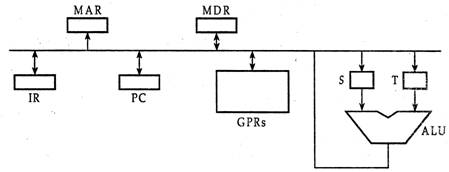

Considere la siguiente ruta de datos de una CPU.

La ALU, el bus y todos los registros en la ruta de datos son de tamaño idéntico. Todas las operaciones, incluido el incremento de la PC y los GPR, deben realizarse en la ALU. Se necesitan dos ciclos de reloj para la operación de lectura de memoria: el primero para cargar la dirección en el MAR y el siguiente para cargar los datos del bus de memoria en el MDR

79.

La instrucción «call Rn, sub» es una instrucción de dos palabras. Suponiendo que PC se incrementa durante el ciclo de búsqueda de la primera palabra de la instrucción, su interpretación de transferencia de registro es

Rn < = PC + 1; PC < = M[PC];

El número mínimo de ciclos de reloj de CPU necesarios durante el ciclo de ejecución de esta instrucción es:

(A) 2

(B) 3

(C) 4

(D) 5

Respuesta: (B)

Explicación: Un ciclo para incrementar PC, un ciclo para cargar PC en MAR, un ciclo para recuperar el contenido de la memoria y cargarlo en la PC.

Publicación traducida automáticamente

Artículo escrito por GeeksforGeeks-1 y traducido por Barcelona Geeks. The original can be accessed here. Licence: CCBY-SA