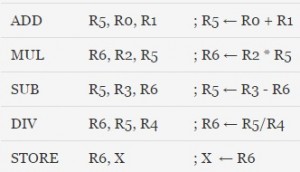

Un procesador segmentado utiliza una secuencia de instrucciones de 4 etapas con las siguientes etapas: obtención de instrucciones (IF), decodificación de instrucciones (ID), ejecución (EX) y reescritura (WB). Las operaciones aritméticas así como las operaciones de carga y almacenamiento se realizan en la etapa EX. La secuencia de instrucciones correspondiente a la declaración X = (S – R * (P + Q))/T se da a continuación. Los valores de las variables P, Q, R, S y T están disponibles en los registros R 0 , R 1 , R 2 , R 3 y R 4 respectivamente, antes de la ejecución de la secuencia de instrucciones.

Las etapas IF, ID y WB toman 1 ciclo de reloj cada una. La etapa EX toma 1 ciclo de reloj cada una para las operaciones ADD, SUB y STORE, y 3 ciclos de reloj cada una para las operaciones MUL y DIV. Se utiliza el reenvío de operandos desde la etapa EX a la etapa ID. El número de ciclos de reloj necesarios para completar la secuencia de instrucciones es

(A) 10

(B) 12

(C) 14

(D) 16

Respuesta: (B)

Explicación:

Esta solución es aportada por

Publicación traducida automáticamente

Artículo escrito por GeeksforGeeks-1 y traducido por Barcelona Geeks. The original can be accessed here. Licence: CCBY-SA