- En varias aplicaciones digitales (por ejemplo: unidad de control cableada) se necesitan señales de control para iniciar, ejecutar y avanzar varias operaciones en una secuencia de tiempo particular.

- Para ello se requieren señales de control y para la generación de señales de control se diseña un circuito contador cuyas salidas se conectan a un decodificador. El decodificador proporciona la señal de control requerida.

- El contador puede ser síncrono o asíncrono.

- El procedimiento para diseñar el contador es el mismo que se refiere a ( this ).

Diagrama de bloques para la generación de señales de control

El diseño de la señal de control puede entenderse considerando el ejemplo.

Ejemplo: generar una señal de control que pueda entregar el siguiente tren de pulsos. El tren de pulsos se repetirá después de 7 pulsos.

Señal de control

Aquí necesitamos generar una señal de control (digamos S) que pueda generar un tren de pulso periódico de 0111001 y luego se repita. El tren de pulsos se repite después de 7 siete pulsos. Por lo tanto, se necesita el contador mod -7. Las salidas del contador Mod-7 se conectarán a un circuito decodificador. Para ello se diseñará un contador mod –7. Se requieren tres cambios de T (porque necesitamos contar hasta 000 a 110, por lo tanto, se necesitan 3 bits).

Para el diseño del contador Mod — N, consulte este artículo .

Diseño para contador mod-7:

aquí Q es el estado anterior y Q* es el estado siguiente.

Tabla de circuito de excitación para mod- 7 Contador

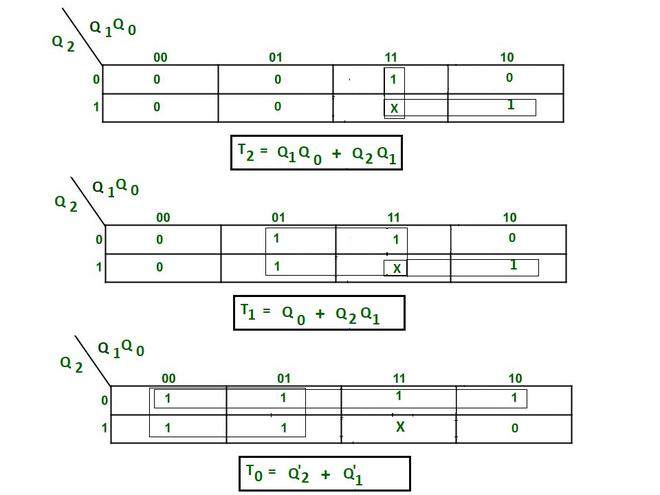

Las expresiones para entradas de flip-flops T obtenidas de los mapas K que se muestran a continuación.

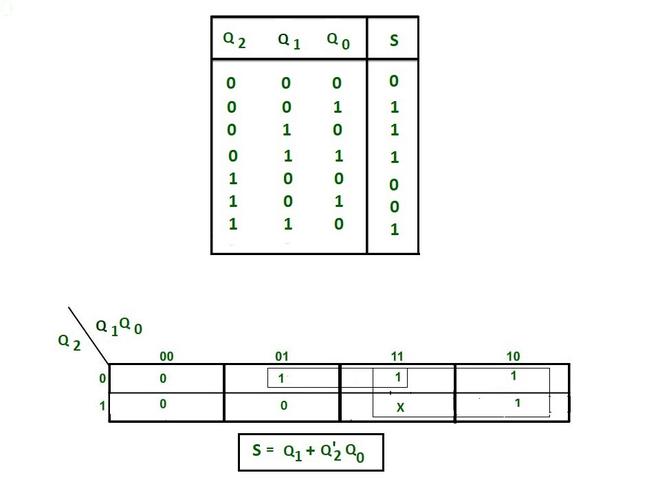

La tabla de verdad para el decodificador se obtiene observando la secuencia de tiempo dada (0111001 ). La expresión simplificada para la salida S del decodificador se obtiene utilizando el mapa K. Los conteos no usados son considerados como no importan.

Cada secuencia de conteo se asigna a un bit de señal de control.

La lógica combinacional del decodificador se puede encontrar resolviendo el mapa K.

La expresión simplificada para el circuito decodificador es S= Q 1 + Q’ 2 Q 0 .

Ejemplo — Cuando estamos en el estado Q 2 =0 Q 1 = 0 Q 0 = 0, entonces el valor de S = 0+0.1= 0.

Diagrama lógico completo con Decoder.

El circuito del decodificador genera una salida después de cada pulso de reloj (flanco -ve disparado). La salida, es decir, S, actuará como señal de control para otros circuitos.

La generación de una señal de control tiene lugar después de cada reloj de flanco negativo y el diagrama de tiempo para dicha señal de control también se puede dibujar como se muestra a continuación. Cada estado del contador se utiliza para generar una señal de control.

Diagrama de tiempo para la generación de la señal de control S por contador

Publicación traducida automáticamente

Artículo escrito por goutamnagpal y traducido por Barcelona Geeks. The original can be accessed here. Licence: CCBY-SA