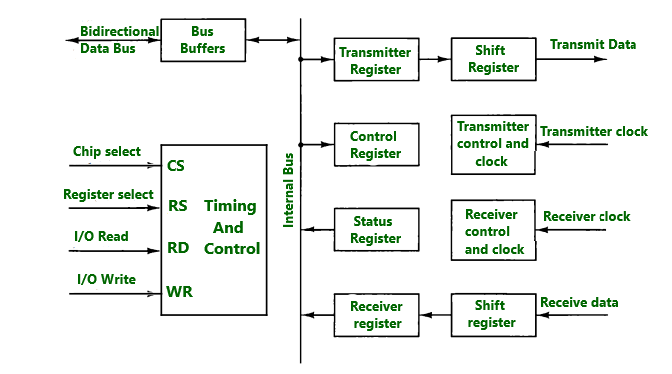

El diagrama de bloques de la interfaz de comunicación asíncrona se muestra arriba. Funciona tanto como transmisor como receptor.

Partes de la interfaz:

la interfaz se inicializa con la ayuda de un bit de control cargado en el registro de control. El registro del transmisor acepta el byte de datos de la CPU a través del bus de datos que luego se transfiere al registro de desplazamiento para la transmisión en serie. La información serial se recibe en otro registro de desplazamiento y se transfiere al registro receptor cuando se acumula un byte de datos completo. Los bits en el registro de estado se utilizan para verificar cualquier error durante la transmisión y para los indicadores de entrada y salida que la CPU puede leer. La entrada de selección de chip (CS) se utiliza para seleccionar la interfaz a través del bus de direcciones. La selección de registro (RS) está asociada con los controles de lectura (RD) y escritura (WR). Dos registros son de solo lectura y escritura.

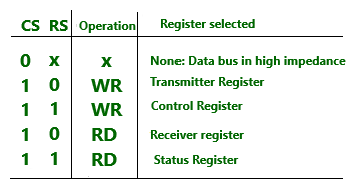

El registro seleccionado es la función del valor RS y el estado RD y WR como se muestra en la siguiente tabla.

Funcionamiento de la interfaz:

la CPU inicializa la interfaz enviando un byte al registro de control. Dos bits en el registro de estado se usan como banderas y un bit se usa para indicar si el registro de transmisión está vacío y otro bit se usa para indicar si el registro del receptor está lleno.

Funcionamiento de la parte del transmisor:

la CPU lee el registro de estado y comprueba el transmisor. Si el transmisor está vacío, la CPU transfiere el carácter al transmisor. El primer bit en el transmisor se establece en 0 para generar un bit de inicio. La transferencia paralela de caracteres tiene lugar desde el registro del transmisor al registro de desplazamiento. A continuación, el transmisor se marca como vacío. La CPU puede transferir otro carácter al registro del transmisor después de verificar la bandera en el registro de estado.

Funcionamiento de la parte del receptor:

la entrada de datos de recepción está en 1 estado cuando la línea está inactiva. El control del receptor supervisa la línea de datos de recepción para detectar la aparición de un bit de inicio. Luego, los bits de carácter se desplazan al registro de desplazamiento una vez que se ha detectado el bit de inicio. Cuando se recibe el bit de parada, el carácter se transfiere en paralelo desde el registro de desplazamiento al registro receptor.

La interfaz comprueba si hay errores durante la transmisión y establece los bits apropiados en el registro de estado. Los tres posibles errores que comprueba la interfaz son el error de paridad, el error de trama y el error de sobreejecución.