El método que se utiliza para transferir información entre el almacenamiento interno y los dispositivos de E/S externos se conoce como interfaz de E/S. La CPU está conectada mediante enlaces de comunicación especiales por los periféricos conectados a cualquier sistema informático. Estos enlaces de comunicación se utilizan para resolver las diferencias entre la CPU y el periférico. Existen componentes de hardware especiales entre la CPU y los periféricos para supervisar y sincronizar todas las transferencias de entrada y salida que se denominan unidades de interfaz.

Modo de transferencia:

La información binaria que se recibe de un dispositivo externo generalmente se almacena en la unidad de memoria. La información que se transfiere desde la CPU al dispositivo externo se origina en la unidad de memoria. La CPU simplemente procesa la información, pero el origen y el destino es siempre la unidad de memoria. La transferencia de datos entre la CPU y los dispositivos de E/S se puede realizar en diferentes modos.

La transferencia de datos hacia y desde los periféricos se puede realizar de cualquiera de las tres formas posibles

- E/S programada.

- E/S iniciada por interrupción.

- Acceso directo a memoria (DMA).

Ahora analicemos cada modo uno por uno.

- E/S programada: Se debe al resultado de las instrucciones de E/S que se escriben en el programa de la computadora. Cada transferencia de elementos de datos se inicia mediante una instrucción en el programa. Por lo general, la transferencia se realiza desde un registro y una memoria de la CPU. En este caso requiere un monitoreo constante por parte de la CPU de los dispositivos periféricos.

Ejemplo de E/S programada: En este caso, el dispositivo de E/S no tiene acceso directo a la unidad de memoria. Una transferencia del dispositivo de E/S a la memoria requiere la ejecución de varias instrucciones por parte de la CPU, incluida una instrucción de entrada para transferir los datos del dispositivo a la CPU y una instrucción de almacenamiento para transferir los datos de la CPU a la memoria. En la E/S programada, la CPU permanece en el ciclo del programa hasta que la unidad de E/S indica que está lista para la transferencia de datos. Este es un proceso que requiere mucho tiempo ya que mantiene innecesariamente ocupada la CPU. Esta situación se puede evitar utilizando una función de interrupción. Esto se discute a continuación.

- E/S iniciada por interrupción: Dado que en el caso anterior vimos que la CPU se mantiene ocupada innecesariamente. Esta situación se puede evitar muy bien mediante el uso de un método controlado por interrupciones para la transferencia de datos. Mediante el uso de funciones de interrupción y comandos especiales para informar a la interfaz que emita una señal de solicitud de interrupción siempre que haya datos disponibles desde cualquier dispositivo. Mientras tanto, la CPU puede continuar con cualquier otra ejecución del programa. Mientras tanto, la interfaz sigue monitoreando el dispositivo. Cada vez que se determina que el dispositivo está listo para la transferencia de datos, inicia una señal de solicitud de interrupción a la computadora. Al detectar una señal de interrupción externa, la CPU detiene momentáneamente la tarea que ya estaba realizando, se bifurca al programa de servicio para procesar la transferencia de E/S y luego regresa a la tarea que estaba realizando originalmente.

Nota: Tanto el método de E/S programada como el de E/S controlada por interrupción requieren la intervención activa del

procesador para transferir datos entre la memoria y el módulo de E/S, y cualquier transferencia de datos debe atravesar

una ruta a través del procesador. Por tanto, estas dos formas de E/S adolecen de dos inconvenientes inherentes.

- La tasa de transferencia de E/S está limitada por la velocidad con la que el procesador puede probar y reparar un

dispositivo. - El procesador está ocupado en la gestión de una transferencia de E/S; se debe ejecutar una serie de instrucciones

para cada transferencia de E/S.

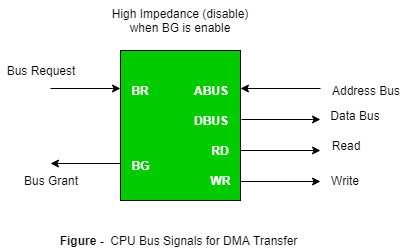

Bus Request: Es utilizado por el controlador DMA para solicitar a la CPU que renuncie al control de los buses.

Bus Grant: es activado por la CPU para informar al controlador DMA externo que los buses están en estado de alta impedancia y que el DMA solicitante puede tomar el control de los buses. Una vez que la DMA ha tomado el control de los buses, transfiere los datos. Esta transferencia puede tener lugar de muchas maneras.

Tipos de transferencia DMA utilizando el controlador DMA:

Transferencia en ráfaga:

DMA devuelve el bus después de completar la transferencia de datos. Se utiliza un registro como conteo de bytes,

que se decrementa para cada transferencia de bytes, y cuando el conteo de bytes llega a cero, el DMAC

liberará el bus. Cuando el DMAC opera en modo ráfaga, la CPU se detiene durante la

transferencia de datos.

Los pasos involucrados son:

- Tiempo de solicitud de concesión de autobús.

- Transfiera todo el bloque de datos a la velocidad de transferencia del dispositivo porque el dispositivo suele ser más lento que la

velocidad a la que se pueden transferir los datos a la CPU. - Libere el control del bus de vuelta a la CPU

Por lo tanto, el tiempo total necesario para transferir los N bytes

= tiempo de solicitud de concesión de bus + (N) * (velocidad de transferencia de memoria) + tiempo de control de liberación del bus.

Where, X µsec =data transfer time or preparation time (words/block) Y µsec =memory cycle time or cycle time or transfer time (words/block) % CPU idle (Blocked)=(Y/X+Y)*100 % CPU Busy=(X/X+Y)*100

Robo cíclico:

un método alternativo en el que el controlador DMA transfiere una palabra a la vez, después de lo cual debe devolver el control de los buses a la CPU. La CPU retrasa su operación solo durante un ciclo de memoria para permitir que la transferencia directa de E/S de memoria «robe» un ciclo de memoria.

Los pasos involucrados son:

- Buffer el byte en el búfer

- Informe a la CPU que el dispositivo tiene 1 byte para transferir (es decir, solicitud de concesión de bus)

- Transferir el byte (a la velocidad del bus del sistema)

- Suelte el control del bus de vuelta a la CPU.

Antes de continuar con la transferencia del siguiente byte de datos, el dispositivo realiza el paso 1 nuevamente para que el bus no esté ocupado y

la transferencia no dependa de la tasa de transferencia del dispositivo.

Por lo tanto, para 1 byte de transferencia de datos, el tiempo necesario para usar el modo de robo de ciclo (T).

= tiempo requerido para concesión de bus + 1 ciclo de bus para transferir datos + tiempo requerido para liberar bus, será

N x T

En el modo de robo de ciclos, siempre seguimos el concepto de canalización de que cuando se transfiere un byte, el dispositivo prepara en paralelo el siguiente byte. «La fracción del tiempo de CPU al tiempo de transferencia de datos» si se le pregunta, entonces se usa el modo de robo de ciclo.

Where, X µsec =data transfer time or preparation time (words/block) Y µsec =memory cycle time or cycle time or transfer time (words/block) % CPU idle (Blocked) =(Y/X)*100 % CPU busy=(X/Y)*100

Modo intercalado: en esta técnica, el controlador DMA se hace cargo del bus del sistema cuando el

microprocesador no lo está utilizando. Un medio ciclo alternativo, es decir, medio ciclo DMA + procesador de medio ciclo.

Nota: En Gate Exam, puede aplicar directamente la fórmula anterior para diferentes modos de transferencia DMA.

Este artículo es una contribución de Namita Singh .

Escriba comentarios si encuentra algo incorrecto o si desea compartir más información sobre el tema tratado anteriormente.

Publicación traducida automáticamente

Artículo escrito por GeeksforGeeks-1 y traducido por Barcelona Geeks. The original can be accessed here. Licence: CCBY-SA