Cuando el microprocesador recibe cualquier señal de interrupción de los periféricos que solicitan sus servicios, detiene su ejecución actual y el control del programa se transfiere a una subrutina generando una señal CALL y después de ejecutar la subrutina generando una señal RET nuevamente, el control del programa es transferido al programa principal desde donde se había detenido.

Cuando el microprocesador recibe señales de interrupción, envía un reconocimiento (INTA) al periférico que solicita su servicio.

Las interrupciones se pueden clasificar en varias categorías en función de diferentes parámetros:

- Interrupciones de hardware y software:

cuando los microprocesadores reciben señales de interrupción a través de los pines (hardware) del microprocesador, se conocen como interrupciones de hardware . Hay 5 interrupciones de hardware en el microprocesador 8085. Ellos son: INTR, RST 7.5, RST 6.5, RST 5.5, TRAMPALas interrupciones de software son aquellas que se insertan entre el programa, lo que significa que son mnemotécnicos del microprocesador. Hay 8 interrupciones de software en el microprocesador 8085. Ellos son: PRIMERA 0, PRIMERA 1, PRIMERA 2, PRIMERA 3, PRIMERA 4, PRIMERA 5, PRIMERA 6, PRIMERA 7 .

- Interrupciones vectorizadas y no vectoriales: las

interrupciones vectorizadas son aquellas que tienen una dirección de vector fija (dirección de inicio de la subrutina) y después de ejecutarlas, el control del programa se transfiere a esa dirección.

Las direcciones vectoriales se calculan mediante la fórmula 8 * TIPO

INTERRUMPIR DIRECCIÓN VECTORIAL TRAMPA (RST 4.5) 24 horas PRIMERA 5.5 2CH PRIMERA 6.5 34 horas PRIMERA 7.5 3CH Para las interrupciones de software, las direcciones de los vectores están dadas por:

INTERRUMPIR DIRECCIÓN VECTORIAL PRIMERA 0 00 horas PRIMERA 1 08 horas PRIMERA 2 10 horas PRIMERA 3 18 horas PRIMERA 4 20 horas PRIMERA 5 28 horas PRIMERA 6 30 horas PRIMERA 7 38 horas Las interrupciones no vectorizadas son aquellas en las que la dirección del vector no está predefinida. El dispositivo de interrupción proporciona la dirección de la subrutina para estas interrupciones. INTR es la única interrupción no vectorizada en el microprocesador 8085.

- Interrupciones enmascarables y no enmascarables: las interrupciones

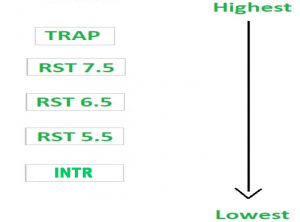

enmascarables son aquellas que el microprocesador puede desactivar o ignorar. Estas interrupciones se activan por flanco o por nivel, por lo que se pueden desactivar. INTR, RST 7.5, RST 6.5, RST 5.5 son interrupciones enmascarables en el microprocesador 8085.Las interrupciones no enmascarables son aquellas que el microprocesador no puede desactivar o ignorar. TRAP es una interrupción no enmascarable. Consta de activación tanto por nivel como por flanco y se utiliza en condiciones críticas de fallo de alimentación.

Prioridad de interrupciones:

cuando el microprocesador recibe múltiples requests de interrupción simultáneamente, ejecutará la solicitud de servicio de interrupción (ISR) de acuerdo con la prioridad de las interrupciones.

Instruction for Interrupts –

- Habilitar interrupción (EI): el flip-flop de habilitación de interrupción se establece y todas las interrupciones se habilitan después de la ejecución de la siguiente instrucción seguida de EI. Ninguna bandera se ve afectada. Después de un restablecimiento del sistema, el flip-flop de habilitación de interrupción se restablece, deshabilitando así las interrupciones. Esta instrucción es necesaria para habilitar nuevamente las interrupciones (excepto TRAP).

- Deshabilitar interrupción (DI): esta instrucción se usa para restablecer el valor del flip-flop habilitado y, por lo tanto, deshabilitar todas las interrupciones. Ninguna bandera se ve afectada por esta instrucción.

- Establecer máscara de interrupción (SIM): se utiliza para implementar las interrupciones de hardware (RST 7.5, RST 6.5, RST 5.5) configurando varios bits para formar máscaras o generar datos de salida a través de la línea de datos de salida en serie (SOD). Primero, el valor requerido se carga en el acumulador, luego la SIM tomará el patrón de bits.

- Máscara de interrupción de lectura (RIM): esta instrucción se utiliza para leer el estado de las interrupciones de hardware (RST 7.5, RST 6.5, RST 5.5) cargando en el registro A un byte que define la condición de los bits de máscara para las interrupciones. También lee la condición del bit SID (Serial Input Data) en el microprocesador.

Publicación traducida automáticamente

Artículo escrito por harshit-chhabra y traducido por Barcelona Geeks. The original can be accessed here. Licence: CCBY-SA