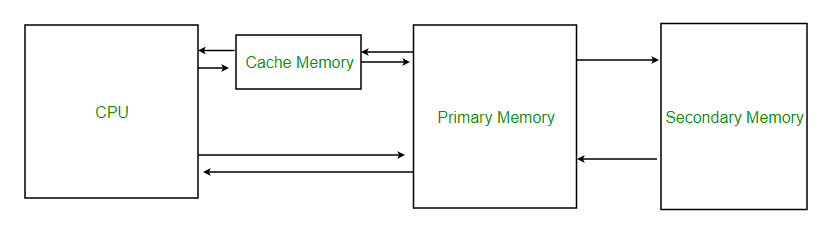

La memoria caché es una memoria especial de muy alta velocidad. Se utiliza para acelerar y sincronizar con CPU de alta velocidad. La memoria caché es más costosa que la memoria principal o la memoria de disco, pero más económica que los registros de la CPU. La memoria caché es un tipo de memoria extremadamente rápido que actúa como un búfer entre la RAM y la CPU. Contiene datos e instrucciones solicitados con frecuencia para que estén disponibles de inmediato para la CPU cuando sea necesario.

La memoria caché se utiliza para reducir el tiempo promedio de acceso a los datos de la memoria principal. La caché es una memoria más pequeña y rápida que almacena copias de los datos de las ubicaciones de la memoria principal que se usan con frecuencia. Hay varios cachés independientes diferentes en una CPU, que almacenan instrucciones y datos.

Niveles de memoria:

- Nivel 1 o Registro:

es un tipo de memoria en la que se almacenan y aceptan datos que se almacenan inmediatamente en la CPU. El registro más utilizado es el acumulador, el contador de programas, el registro de direcciones, etc. - Memoria de nivel 2 o caché:

es la memoria más rápida que tiene un tiempo de acceso más rápido donde los datos se almacenan temporalmente para un acceso más rápido. - Nivel 3 o memoria principal:

es la memoria en la que la computadora funciona actualmente. Es de tamaño pequeño y una vez que se apaga, los datos ya no permanecen en esta memoria. - Nivel 4 o memoria secundaria:

es una memoria externa que no es tan rápida como la memoria principal, pero los datos permanecen permanentemente en esta memoria.

Rendimiento de la memoria caché:

cuando el procesador necesita leer o escribir una ubicación en la memoria principal, primero busca una entrada correspondiente en la memoria caché.

- Si el procesador encuentra que la ubicación de la memoria está en el caché, se ha producido un golpe de caché y se leen los datos del caché.

- Si el procesador no encuentra la ubicación de la memoria en la memoria caché, se ha producido una falta de memoria caché . Para una falla de caché, el caché asigna una nueva entrada y copia los datos de la memoria principal, luego la solicitud se cumple a partir del contenido del caché.

El rendimiento de la memoria caché se mide con frecuencia en términos de una cantidad denominada tasa de aciertos.

Hit ratio = hit / (hit + miss) = no. of hits/total accesses

Podemos mejorar el rendimiento de la caché utilizando un tamaño de bloque de caché más alto, una mayor asociatividad, reducir la tasa de fallas, reducir la penalización por fallas y reducir el tiempo para acertar en la caché.

Mapeo de caché:

hay tres tipos diferentes de mapeo que se utilizan para la memoria caché, que son los siguientes: mapeo directo, mapeo asociativo y mapeo asociativo de conjuntos. Estos se explican a continuación.

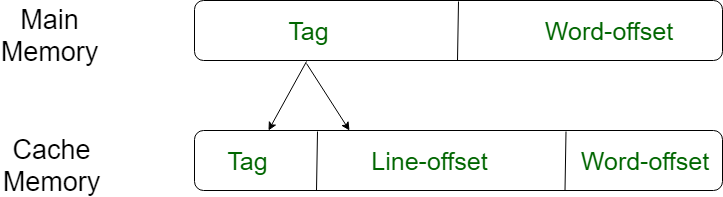

- Mapeo directo:

la técnica más simple, conocida como mapeo directo, mapea cada bloque de memoria principal en una sola línea de caché posible. o

En Mapeo directo, asigne cada bloque de memoria a una línea específica en el caché. Si una línea está previamente ocupada por un bloque de memoria cuando se necesita cargar un nuevo bloque, el bloque antiguo se desecha. Un espacio de direcciones se divide en dos partes, un campo de índice y un campo de etiqueta. El caché se utiliza para almacenar el campo de la etiqueta, mientras que el resto se almacena en la memoria principal. El rendimiento del mapeo directo es directamente proporcional a la tasa de aciertos.i = j modulo m where i=cache line number j= main memory block number m=number of lines in the cache

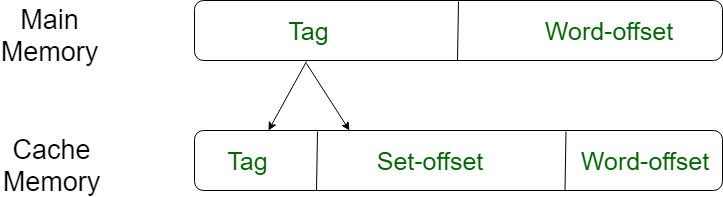

A los efectos del acceso a la memoria caché, cada dirección de la memoria principal puede verse como compuesta por tres campos. Los bits w menos significativos identifican una palabra o byte único dentro de un bloque de memoria principal. En la mayoría de las máquinas contemporáneas, la dirección está a nivel de byte. Los bits s restantes especifican uno de los 2 bloques s de la memoria principal. La lógica de caché interpreta estos s bits como una etiqueta de sr bits (la porción más significativa) y un campo de línea de r bits. Este último campo identifica una de las m=2 r líneas del caché.

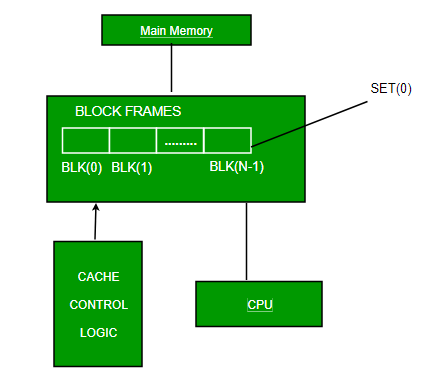

- Mapeo asociativo:

en este tipo de mapeo, la memoria asociativa se usa para almacenar contenido y direcciones de la palabra de memoria. Cualquier bloque puede ir a cualquier línea del caché. Esto significa que los bits de identificación de palabra se utilizan para identificar qué palabra del bloque se necesita, pero la etiqueta se convierte en todos los bits restantes. Esto permite la colocación de cualquier palabra en cualquier lugar de la memoria caché. Se considera que es la forma de mapeo más rápida y flexible.

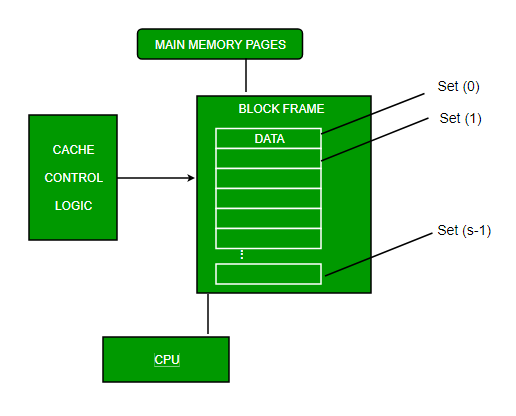

- Mapeo asociativo de conjuntos:

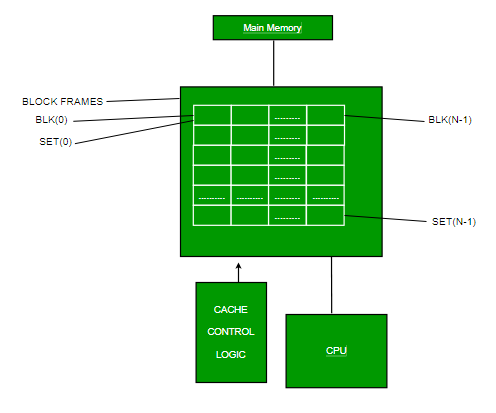

esta forma de mapeo es una forma mejorada de mapeo directo donde se eliminan los inconvenientes del mapeo directo. El conjunto asociativo aborda el problema de la posible hiperpaginación en el método de mapeo directo. Lo hace diciendo que en lugar de tener exactamente una línea a la que un bloque puede asignarse en el caché, agruparemos algunas líneas para crear un conjunto . Luego, un bloque en la memoria puede asignarse a cualquiera de las líneas de un conjunto específico. El mapeo asociativo de conjuntos permite que cada palabra que está presente en el caché pueda tener dos o más palabras en la memoria principal para la misma dirección de índice. Establecer asignación de caché asociativa combina lo mejor de las técnicas de asignación de caché directa y asociativa.En este caso, la memoria caché consta de una serie de conjuntos, cada uno de los cuales consta de una serie de líneas. las relaciones son

m = v * k i= j mod v where i=cache set number j=main memory block number v=number of sets m=number of lines in the cache number of sets k=number of lines in each set

Aplicación de memoria caché –

- Por lo general, la memoria caché puede almacenar una cantidad razonable de bloques en un momento dado, pero esta cantidad es pequeña en comparación con la cantidad total de bloques en la memoria principal.

- La correspondencia entre los bloques de memoria principal y los de la memoria caché se especifica mediante una función de mapeo.

Tipos de caché –

- Caché

principal: siempre se encuentra un caché principal en el chip del procesador. Esta caché es pequeña y su tiempo de acceso es comparable al de los registros del procesador. - Caché

secundario: el caché secundario se coloca entre el caché principal y el resto de la memoria. Se denomina caché de nivel 2 (L2). A menudo, la memoria caché de nivel 2 también se encuentra en el chip del procesador.

Localidad de referencia:

dado que el tamaño de la memoria caché es menor en comparación con la memoria principal. Entonces, para verificar qué parte de la memoria principal debe tener prioridad y cargarse en caché, se decide según la localidad de referencia.Tipos de Localidad de referencia

- Localidad espacial de referencia

Esto dice que existe la posibilidad de que el elemento esté presente en las proximidades del punto de referencia y la próxima vez, si se busca de nuevo, más cerca del punto de referencia. - Localidad temporal de referencia

En este algoritmo se utilizará el menos utilizado recientemente. Siempre que ocurra una falla de página dentro de una palabra, no solo se cargará la palabra en la memoria principal, sino que se cargará la falla de página completa porque la regla de localidad espacial de referencia dice que si está refiriendo cualquier palabra, la siguiente palabra se referirá en su registro, por eso cargamos tabla de página completa para que se cargue el bloque completo.

Preguntas de práctica GATE –

Que-1: una computadora tiene una caché de datos de reescritura asociativa de 4 vías de 256 KByte con un tamaño de bloque de 32 bytes. El procesador envía direcciones de 32 bits al controlador de caché. Cada entrada de directorio de etiquetas de caché contiene, además de la etiqueta de dirección, 2 bits válidos, 1 bit modificado y 1 bit de reemplazo. El número de bits en el campo de etiqueta de una dirección es

(A) 11 (B) 14 (C) 16 (D) 27

Respuesta: (C)

Explicación: https://www.geeksforgeeks.org/gate-gate-cs-2012-question-54/

Que-2: Considere los datos dados en la pregunta anterior. El tamaño del directorio de etiquetas de caché es

(A) 160 Kbits (B) 136 bits (C) 40 Kbits (D) 32 bits

Respuesta: (A)

Explicación: https://www.geeksforgeeks.org/gate-gate-cs-2012-question-55/

Que-3: una memoria caché de reescritura de asignación directa de 8 KB se organiza en varios bloques, cada uno con un tamaño de 32 bytes. El procesador genera direcciones de 32 bits. El controlador de caché mantiene la información de la etiqueta para cada bloque de caché que comprende lo siguiente.

1 Valid bit 1 Modified bit

Tantos bits como el mínimo necesario para identificar el bloque de memoria mapeado en la caché. ¿Cuál es el tamaño total de la memoria necesaria en el controlador de caché para almacenar metadatos (etiquetas) para el caché?

(A) 4864 bits (B) 6144 bits (C) 6656 bits (D) 5376 bits

Respuesta: (D)

Explicación: https://www.geeksforgeeks.org/gate-gate-cs-2011-question-43/

Artículo aportado por Pooja Taneja y Vaishali Bhatia . Escriba comentarios si encuentra algo incorrecto o si desea compartir más información sobre el tema tratado anteriormente.

Publicación traducida automáticamente

Artículo escrito por GeeksforGeeks-1 y traducido por Barcelona Geeks. The original can be accessed here. Licence: CCBY-SA