Según desde dónde se recuperan los operandos en un procesador vectorial, las computadoras vectoriales revestidas se clasifican en dos configuraciones arquitectónicas:

- Arquitectura de memoria a memoria:

en la arquitectura de memoria a memoria, los operandos de origen, los resultados intermedios y finales se recuperan (leen) directamente de la memoria principal. Para las instrucciones de vector de memoria a memoria, se debe especificar la información de la dirección base, el desplazamiento, el incremento y la longitud del vector para permitir flujos de transferencias de datos entre la memoria principal y las canalizaciones. Los procesadores como TI-ASC, CDC STAR-100 y Cyber-205 tienen instrucciones vectoriales en formatos de memoria a memoria. Los puntos principales sobre la arquitectura de memoria a memoria son:- No hay limitación de tamaño.

- La velocidad es comparativamente lenta en esta arquitectura

- Arquitectura de

registro a registro: en la arquitectura de registro a registro, los operandos y los resultados se recuperan indirectamente de la memoria principal mediante el uso de una gran cantidad de registros vectoriales o registros escalares. Los procesadores como Cray-1 y Fujitsu VP-200 usan instrucciones vectoriales en formatos de registro a registro. Los puntos principales sobre la arquitectura de registro a registro son:- Registro para registrar la arquitectura tiene un tamaño limitado.

- La velocidad es muy alta en comparación con la arquitectura de memoria a memoria.

- El costo del hardware es alto en esta arquitectura.

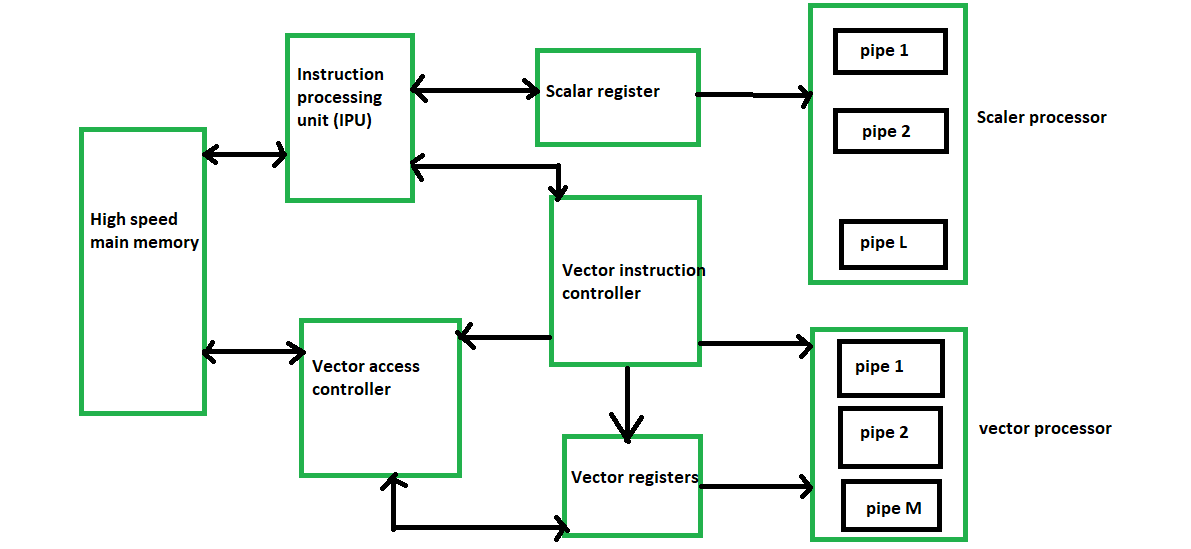

A continuación se muestra un diagrama de bloques de una computadora vectorial moderna de tuberías múltiples:

Un típico procesador de vectores revestido de tubería.

Publicación traducida automáticamente

Artículo escrito por SUDIPTADANDAPAT y traducido por Barcelona Geeks. The original can be accessed here. Licence: CCBY-SA