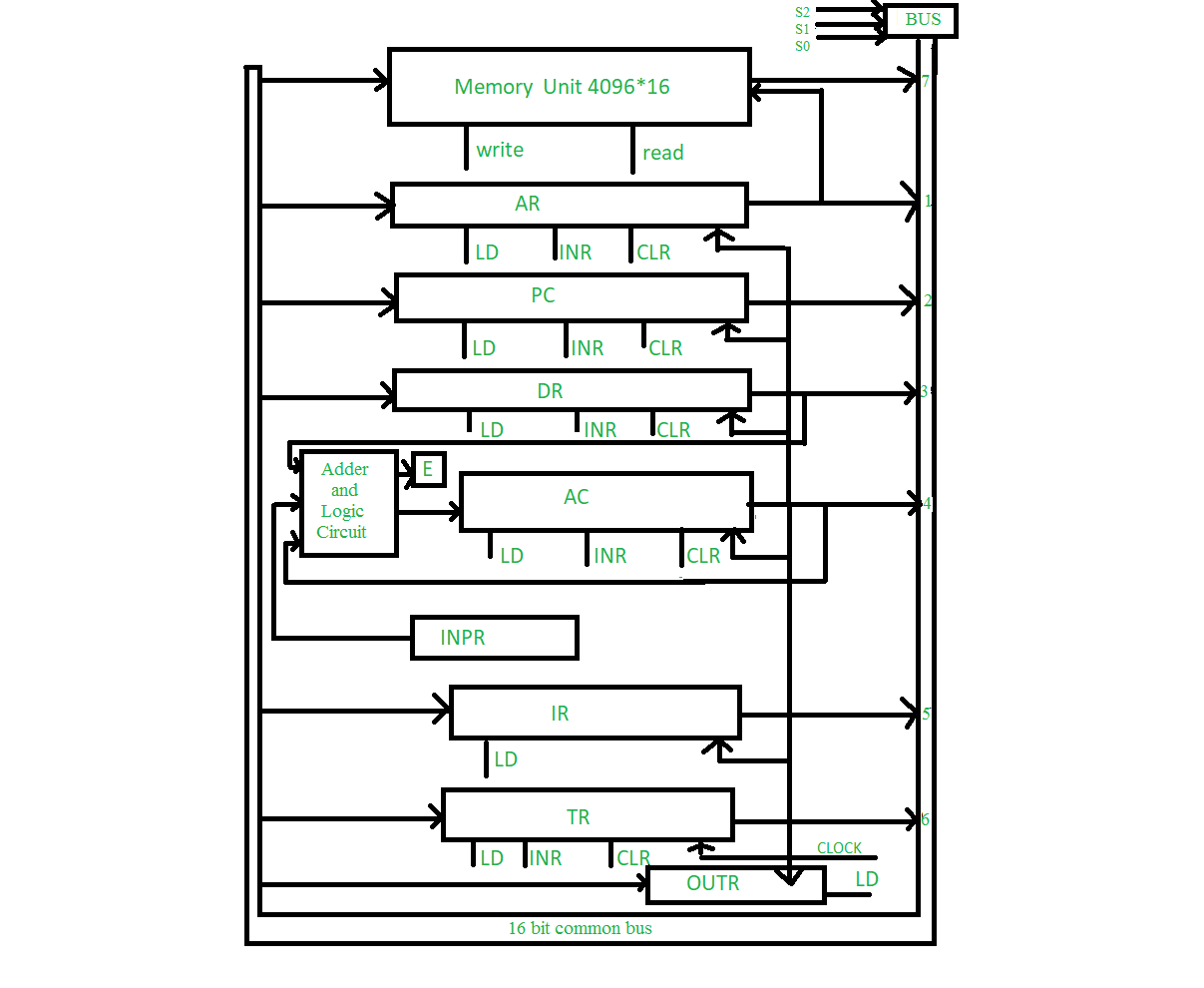

Estudiaremos el sistema de bus común de una computadora muy básica en este artículo. Una computadora básica tiene 8 registros, unidad de memoria y una unidad de control. El diagrama del sistema de bus común es como se muestra a continuación.

Conexiones:

Las salidas de todos los registros excepto el OUTR (registro de salida) se conectan al bus común. La salida seleccionada depende del valor binario de las variables S2, S1 y S0. Las líneas del bus común están conectadas a las entradas de los registros y la memoria. Un registro recibe la información del bus cuando se activa su entrada LD (carga), mientras que en el caso de la memoria, la entrada Write debe estar habilitada para recibir la información. El contenido de la memoria se coloca en el bus cuando se activa su entrada de lectura.

Varios Registros:

4 registros DR, AC, IR y TR tienen 16 bits y 2 registros AR y PC tienen 12 bits. INPR y OUTR tienen 8 bits cada uno. El INPR recibe el carácter del dispositivo de entrada y lo entrega al AC mientras que el OUTR recibe el carácter del AC y lo transfiere al dispositivo de salida. 5 registros tienen 3 entradas de control LD (carga), INR (incremento) y CLR (borrar). Estos tipos de registros son similares a un contador binario.

| Abreviatura | Registrar nombre |

|---|---|

| SALIDA | Registro de salida |

| TR | registro temporal |

| infrarrojos | Registro de instrucciones |

| INPR | registro de entrada |

| C.A. | Acumulador |

| DR | registro de datos |

| ordenador personal | Contador de programa |

| Arkansas | Registro de direcciones |

Circuito sumador y lógico :

El circuito sumador y lógico proporciona las 16 entradas de CA. Este circuito tiene 3 juegos de entradas. Un conjunto proviene de las salidas de AC que implementa microoperaciones de registro. El otro conjunto proviene del DR (registro de datos) que se utilizan para realizar microoperaciones aritméticas y lógicas. El resultado de estas operaciones se envía a AC mientras que el acarreo final se almacena en E como se muestra en el diagrama. El tercer conjunto de entradas es del INPR.

Nota:

El contenido de cualquier registro se puede colocar en el bus común y se puede realizar una operación en el sumador y el circuito lógico durante el mismo ciclo de reloj.