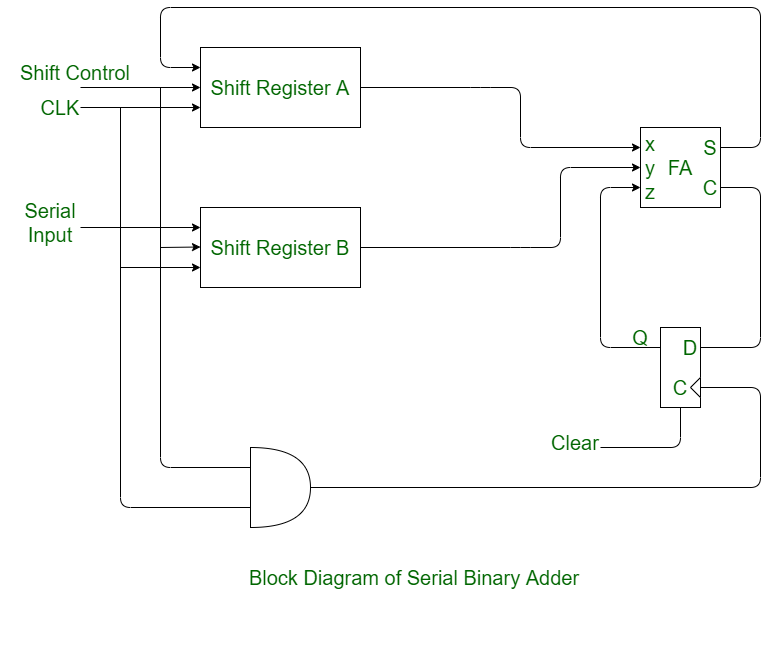

El sumador binario serial es un circuito lógico combinacional que realiza la suma de dos números binarios en forma serial. El sumador binario en serie realiza sumas bit a bit. Se utilizan dos registros de desplazamiento para almacenar los números binarios que se van a sumar.

Se usa un solo sumador completo para agregar un par de bits a la vez junto con el acarreo. La salida de acarreo del sumador completo se aplica a un flip-flop D. Después de esa salida, se usa como acarreo para los siguientes bits significativos. El bit de suma de la salida del sumador completo se puede transferir a un tercer registro de desplazamiento.

Diagrama de bloques del sumador binario en serie:

Registros de desplazamiento :

el registro de desplazamiento es un grupo de flip flops que se utiliza para almacenar múltiples bits de datos. Hay dos registros de desplazamiento utilizados en el sumador binario en serie. En un registro de desplazamiento se almacena el sumando y en otro registro de desplazamiento se almacena el sumando.

Sumador completo :

el sumador completo es el circuito combinacional que toma tres entradas y da dos salidas como suma y acarreo. El circuito agrega un par a la vez con la ayuda de este.

Flip-flop D :

la salida de acarreo del sumador completo se aplica en el flip-flop D. Además, la salida del flip-flop D se usa como entrada de acarreo para el siguiente par de bits significativos.

Proceso de trabajo: El

siguiente es el procedimiento de suma utilizando el sumador binario en serie:

- Paso 1:

Los dos registros de desplazamiento A y B se utilizan para almacenar los números que se agregarán. - Paso 2:

Se usa un solo sumador completo para agregar un par de bits a la vez junto con el acarreo. - Paso 3:

El contenido de los registros de desplazamiento se desplaza de izquierda a derecha y su salida a partir de ayb se alimenta a un único sumador completo junto con la salida del flip-flop de acarreo al aplicar cada pulso de reloj. - Paso 4:

La salida de suma del sumador completo se alimenta al bit más significativo del registro de suma. - Paso 5:

El contenido del registro de suma también se desplaza hacia la derecha cuando se aplica el pulso de reloj. - Paso 6:

Después de aplicar cuatro pulsos de reloj, la suma de los contenidos de dos registros (A y B) se almacena en el registro de suma.