Full Adder es el sumador que suma tres entradas y produce dos salidas. Las primeras dos entradas son A y B y la tercera entrada es un acarreo de entrada como C-IN. El acarreo de salida se designa como C-OUT y la salida normal se designa como S, que es SUM. Una lógica de sumador completa está diseñada de tal manera que puede tomar ocho entradas juntas para crear un sumador de un byte y conectar en cascada el bit de acarreo de un sumador a otro. usamos un sumador completo porque cuando hay un bit de arrastre disponible, se debe usar otro sumador de 1 bit ya que un medio sumador de 1 bit no toma un bit de arrastre. Un sumador completo de 1 bit suma tres operandos y genera resultados de 2 bits.

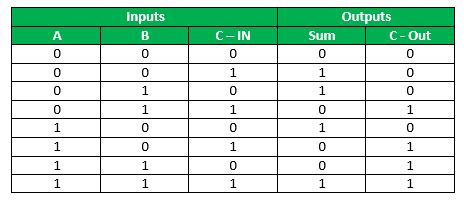

Full Adder Truth Table:

Full Adder Truth Table:

Expresión lógica para SUMA: = A’ B’ C-IN + A’ B C-IN’ + A B’ C-IN’ + AB C-IN = C-IN (A’ B’ + AB) + C-IN’ (A’ B + A B’) = C-IN XOR (A XOR B) = (1,2,4,7)

Expresión lógica para C-SALIDA: = A’ B C-ENTRADA + A B’ C-ENTRADA + AB C-ENTRADA’ + AB C-ENTRADA = AB + B C-ENTRADA + A C-ENTRADA = (3,5,6 ,7)

Otra forma en la que se puede implementar C-OUT: = AB + A C-IN + B C-IN (A + A’) = AB C-IN + AB + A C-IN + A’ B C-IN = AB (1 +C-IN) + A C-IN + A’ B C-IN = AB + A C-IN + A’ B C-IN = AB + A C-IN (B + B’) + A’ B C-IN = AB C-IN + AB + A B’ C-IN + A’ B C-IN = AB (C-IN + 1) + A B’ C-IN + A’ B C-IN = AB + A B’ C-IN + A’ B C-IN = AB + C-IN (A’ B + A B’)

Por lo tanto COUT = AB + C-IN (A EX – O B)

Circuito lógico sumador completo.

Implementación de Full Adder usando Half Adder:

Se requieren 2 medios sumadores y una puerta OR para implementar un sumador completo.

Con este circuito lógico, se pueden sumar dos bits, tomando un acarreo del siguiente orden de magnitud inferior y enviando un acarreo al siguiente orden de magnitud superior.

Implementación de Full Adder usando puertas NAND:  Implementación de Full Adder usando puertas NOR:

Implementación de Full Adder usando puertas NOR:

Se requieren un total de 9 puertas NOR para implementar un sumador completo.  En la expresión lógica anterior, se reconocerían las expresiones lógicas de un medio sumador de 1 bit. Se puede lograr un sumador completo de 1 bit conectando en cascada dos medios sumadores de 1 bit.

En la expresión lógica anterior, se reconocerían las expresiones lógicas de un medio sumador de 1 bit. Se puede lograr un sumador completo de 1 bit conectando en cascada dos medios sumadores de 1 bit.

Publicación traducida automáticamente

Artículo escrito por GeeksforGeeks-1 y traducido por Barcelona Geeks. The original can be accessed here. Licence: CCBY-SA